DAT110:

Methods for Electronic System Design and Verification

Course Overview 2015

|

|

This course overview will remain static throughout the Methods course in Q2.

The PingPong system will be used for all student-teacher interaction and

will contain all news, lectures, etc.

Follow this link

for the PingPong course event which will be active right before Q2.

The first event of the course is Lecture 1 on Tuesday Nov 3, 9-12, in EL42 (notice

the starting time).

GENERAL:

- Aim:

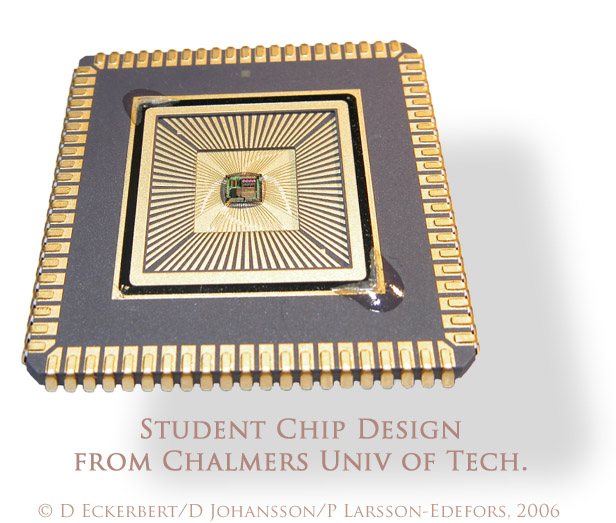

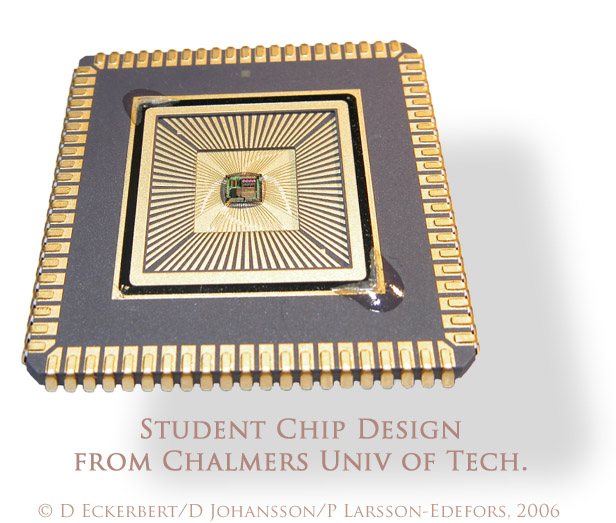

In light of the fact that we can integrate billions of transistors on a single integrated

circuit, electronic system designers are forced to make use of computer-aided design tools,

so-called Electronic Design Automation (EDA) tools, to manage design complexity and to

meet, for example, strict timing, power dissipation and time-to-market budgets. Thus, apart

from having skills in each of the abstraction levels, like circuit, logic, and architecture

design, an electronic system designer must have a thorough understanding of design and

verification methods that span the different abstraction levels and the algorithms that are

leveraged inside the EDA tools.

The purpose of this course is to strengthen the student's knowledge in EDA-based design and

verification methods and to make the student proficient in utilizing the right EDA tools,

in the right context and in the right sequence.

- Pedagogics:

The pedagogical concept of the course rests on three cornerstones:

- lectures: these mainly supply the design and verification context of advanced

electronic systems containing software and hardware.

- lab exercises: these offer comprehensive hands-on training on industrially

relevant design and verification problems using state-of-the-art EDA systems (from Cadence and Synopsys).

- term paper work: this gives the student an opportunity to study state-of-the-art

research-level texts, which allows the student to focus on an appropriate and interesting

technical area and at the same time obtain training in reading research papers and practice

scientific writing.

Written and oral presentation is stimulated through the requirement for a lab

report, and the continuous work with term papers and subsequent presentations.

- Learning Outcomes:

After the completion of this course, the student should be able to

- describe the algorithmic principles of a number of important EDA concepts, such as

behavioral and logic synthesis, logic simulation, static timing analysis, timing

closure and power dissipation analysis

- describe contemporary EDA design flows and their fundamental weaknesses and strengths

- apply appropriate EDA tools to electronic system design and verification problems

- perform timing-driven synthesis and power dissipation analysis for digital circuits

- critically and systematically integrate knowledge, to model, simulate, and evaluate

features of digital ASIC design flows

- communicate his/her conclusions of laboratory work and in-depth term paper studies,

and the knowledge and rationale underpinning these, clearly and unambiguously

- Other Sources of Information:

This is a compulsory course in Q2 of the first year of the Master programme

Embedded Electronic System Design (EESD). You can find further information on the course

and its pedagogical context by following the links below:

TEACHERS:

EXAMINATION:

- The examination is made up of two parts:

- Lab exercises, including synthesis and place-and-route for ASICs: 60% of total course grade

is based on quality of preparation, VHDL handins, log books and lab report

- Term paper work (in teams of 3 students) on selected topics, including a term paper report

and an oral presentation: 40% of total course grade is based on quality of term paper report and oral presentation

TEXTBOOK:

LABS:

- Lab hall: 4220.

- For lab groups, consult PingPong in the end of SW1.

SCHEDULE: