## A Slightly Revised Tutorial on Lava: A Hardware Description and Verification System

Koen Claessen koen@cs.chalmers.se Mary Sheeran ms@cs.chalmers.se

May 3, 2007

# Contents

| 1 | Intr           | oduction                                 | 4  |

|---|----------------|------------------------------------------|----|

| 2 | $\mathbf{Get}$ | ting Started                             | 6  |

|   | 2.1            | Your First Circuit                       | 6  |

|   | 2.2            | The Lava Interpreter                     | 7  |

|   | 2.3            | Your Second Circuit                      | 8  |

|   | 2.4            | Generating VHDL                          | 10 |

|   | 2.5            | Exercises                                | 12 |

| 3 | Big            | ger Circuits                             | 15 |

|   | 3.1            | Recursion over Lists                     | 15 |

|   |                | 3.1.1 Generating VHDL for a binary adder | 16 |

|   | 3.2            | Connection Patterns                      | 16 |

|   | 3.3            | Arithmetic                               | 19 |

|   | 3.4            | Exercises                                | 21 |

| 4 | Ver            | ification                                | 23 |

|   | 4.1            | Simple Properties                        | 23 |

|   | 4.2            | Quantification                           | 24 |

|   | 4.3            | General Properties                       | 25 |

|   | 4.4            | Helping Verification                     | 25 |

|   | 4.5            | Exercises                                | 27 |

| 5 | Seq            | uential Circuits                         | 28 |

|   | 5.1            | The Delay Component                      | 28 |

|   | 5.2            | Multiple Delays                                                                         | 29         |

|---|----------------|-----------------------------------------------------------------------------------------|------------|

|   | 5.3            | Counters                                                                                | <b>3</b> 0 |

|   | 5.4            | Sequentialization                                                                       | 30         |

|   | 5.5            | Variations on rowSeq                                                                    | 31         |

|   | 5.6            | Exercises                                                                               | 32         |

| 6 | Seq            | uential Verification                                                                    | 34         |

|   | 6.1            | Sequential Safety Properties                                                            | 34         |

|   | 6.2            | Sequential Logic                                                                        | 35         |

|   | 6.3            | Verification                                                                            | 35         |

|   | 6.4            | $In  duction  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 36         |

|   | 6.5            | Induction With Depth $\ldots$                                                           | 37         |

|   | 6.6            | Induction With Restricted States                                                        | 40         |

|   | 6.7            | Exercises                                                                               | 41         |

| 7 | Tin            | e Transformations                                                                       | 43         |

|   | 7.1            | Timing Issues                                                                           | 43         |

|   | 7.2            | Slowing Down                                                                            | 44         |

|   | 7.3            | Speeding Up                                                                             | 47         |

|   | 7.4            | Exercises                                                                               | 48         |

| 8 | Mo             | re connection patterns                                                                  | 50         |

|   | 8.1            | Connection patterns revisited                                                           | 50         |

|   | 8.2            | Tree shaped circuits                                                                    | 53         |

|   | 8.3            | Describing Butterfly Circuits                                                           | 55         |

|   | 8.4            | Batcher's Bitonic Merger                                                                | 59         |

|   | 8.5            | Exercises                                                                               | 61         |

| 9 | $\mathbf{Syn}$ | thesizing Lava Circuits                                                                 | 64         |

|   | 9.1            | State Machines                                                                          | 64         |

|   | 9.2            | Behavioral Descriptions                                                                 | 68         |

|   | 9.3            | Exercises                                                                               | 72         |

|   |                |                                                                                         |            |

| 10 Types                                                                                     | 7 | 73 |  |  |  |  |  |

|----------------------------------------------------------------------------------------------|---|----|--|--|--|--|--|

| 10.1 Signals and Circuits                                                                    |   | 73 |  |  |  |  |  |

| 10.2 Connection Patterns                                                                     | ' | 74 |  |  |  |  |  |

| 10.3 Overloading                                                                             |   | 74 |  |  |  |  |  |

| A Quick Reference Guide                                                                      | 5 | 77 |  |  |  |  |  |

| A.1 The lava command                                                                         |   | 77 |  |  |  |  |  |

| A.2 Logical Gates                                                                            |   | 77 |  |  |  |  |  |

| A.3 Arithmetical Gates                                                                       |   | 78 |  |  |  |  |  |

| A.4 Generic Gates                                                                            |   | 79 |  |  |  |  |  |

| A.5 Module: Patterns $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |   | 79 |  |  |  |  |  |

| A.6 Module: Arithmetic                                                                       |   | 80 |  |  |  |  |  |

| A.7 Module: SequentialCircuits                                                               |   | 81 |  |  |  |  |  |

| A.8 Interpretations                                                                          |   | 81 |  |  |  |  |  |

| A.9 Errors                                                                                   |   | 82 |  |  |  |  |  |

| B Answers                                                                                    | 8 | 84 |  |  |  |  |  |

| Bibliography                                                                                 |   |    |  |  |  |  |  |

| Index                                                                                        | ( | 95 |  |  |  |  |  |

## Chapter 1

# Introduction

Lava is an experimental tool for hardware design and verification. Using Lava, one can describe circuits using a simple functional hardware description language. The descriptions are short and sweet, and do not suffer from the verbosity of more standard hardware description languages (HDLs) like VHDL and Verilog. On the other hand, we cannot express the same things as in these large, expressive (and complicated) languages. For example, we cannot express low level details about timing. What we can express very nicely, though, is the ways in which circuits are built from sub-circuits. Lava facilitates the description of connection patterns so that they are easily reusable. For some kinds of circuits, for example in signal processing, this is exactly what we want to do. Lava also provides many different ways of analysing our circuit descriptions. We can simulate circuits, just as with more standard HDLs, but we can also use symbolic methods to generate input to analysis tools such as automatic theorem provers and model checkers. Indeed, the same methods are used to generate structural VHDL from Lava circuit descriptions. Our aim in this tutorial is to gently introduce this new style of circuit design and analysis, by means of examples.

Lava is used at Chalmers as a platform for experiments in the formal verification of hardware [3, 2]. (Note, however, that both of these references are about an older version of Lava, in which circuit descriptions are a bit more complicated.) Satnam Singh, on the other hand, uses Lava in real industrial design projects at Xilinx Inc., one of the main suppliers of Field Programmable Gate Arrays (FPGAs). In particular, Lava has been used with great success in the development of FPGA cores such as filters and Bezier curve drawing circuits, and of customer applications such as digital signal processing for high speed networks and for high performance graphics applications.

Lava really consists of a simple hardware description language embedded in the powerful functional programming language Haskell. So it can be seen as a domain specific language embedded in a general purpose programming language. We describe circuits by writing Haskell programs – and the Lava system itself consists of a set of Haskell modules that give the user various facilities. The embedded language is quite similar to the Lustre synchronous dataflow language [6]. The idea of using a functional programming language to describe hardware was first proposed in the early eighties [13, 14, 7], and there has been quite a lot of work in the area since then [15, 16, 10, 12, 11, 5]. Our intention in building the Lava system (together with Singh) is to provide a tool that demonstrates the feasibility of doing circuit design and analysis using a functional language.

The main idea in Lava is that a single circuit description can be analysed in a variety of different ways, by giving different interpretations to its components (and sometimes even to its connection patterns). The simplest of these interpretations gives us ordinary simulation. But we can do much more. We can allow symbolic rather than concrete data to flow in the circuit, and in this way collect information about the circuit in various different ways. For example, we can run the circuit on symbolic data and produce expressions on the outputs that indicate how each output is related to the inputs. This can be useful when developing a first implementation. However, the expressions can get too large for humans to interpret. Then, we hook up external analysis tools, such as automatic theorem provers, to help us to analyse our circuits. When we hook up to external theorem provers, we are actually using Haskell as a proof scripting language. This turns out to be very convenient. Similarly, when we hook up to other external tools, such as VHDL-based CAD tools, we use Haskell as a scripting language. One way to view the Lava system is as a tool for linking together and controlling other tools in a unified way! Thus Haskell is used not only to construct circuit descriptions but also to control the tools that process those descriptions. The user sees only one language, rather than having to work with many, as is more usual in the CAD world.

This tutorial introduces the style of circuit description used in Lava, by means of very simple examples. It emphasises the way in which Lava *combinators* can be used to capture common interconnection patterns. It shows the three most important *interpretations* or circuit analysis methods – simulation, generation of VHDL code, and generation of logical formulas for input to theorem provers. After working through the tutorial, you should understand how to describe and analyse simple combinational and sequential circuits using Lava. We hope that the quick reference sections at the back of the tutorial will also help you to get started.

## Chapter 2

# **Getting Started**

In this chapter, we show how to describe some simple circuits in the Lava system, and run the interpreter on them.

### 2.1 Your First Circuit

To make a first circuit description, start up the text editor of your choice, and create a text file called First.hs, for example. Lava file names have the extension .hs.

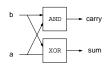

We are going to define a so-called *half adder* (see figure 2.1). A half adder is a component that is for example used in the implementation of a binary adder. It takes as an input two bits, and adds them up. The result is a *sum* and a *carry* bit. A half adder is usually realized using one **and** and one **xor** gate.

Here is how we define a half adder halfAdd in Lava.

import Lava

halfAdd (a, b) = (sum, carry)

where

sum = xor2 (a, b)

carry = and2 (a, b)

We import a module called Lava, which defines a number of operations that we can use to build circuits. Notably, it contains the definitions of the gates xor2 and and2. Appendix A contains a list of such predefined operations.

Note that the order of definitions after a **where** does not matter! Since these circuit components act in parallel, we could just as well have put them the other way around.

Figure 2.1: A half adder.

### 2.2 The Lava Interpreter

During the development of a collection of circuits, we mainly use the Lava *interpreter*. This is actually the Haskell interpreter Hugs [8]. The command is lava.

% lava -- Lava2000 -----

Prelude>

We can use the interpreter to load different modules with circuit definitions, and to type in commands that we want to execute.

If we type in the half adder definition in the file First.hs, we can load it in the interpreter, using the command :1:

Prelude> :l First.hs

Reading file "First.hs":

First.hs Main>

One of the things we can do with a circuit is to simulate it. Simulation is done in Lava with the operation simulate. It takes two arguments; one is the circuit to simulate (in this case halfAdd), and the other is the input to the circuit (in this case a pair of bits).

Main> simulate halfAdd (low,low) (low, low) Main> simulate halfAdd (high,high) (low, high)

If we make any changes to the file with our circuit definitions, we can type the reload command :r in the interpreter:

Main> *:r* ... Main>

The changes are now updated. If you ever want to exit from the interpreter, you can use the :q command.

Main> :q [Leaving Hugs] %

#### 2.3 Your Second Circuit

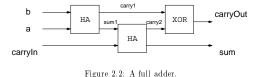

You guessed it! Your second circuit is going to be a *full adder* (see figure 2.2), a component fullAdd that consists of two half adders. To define it, add the following definition to the file First.hs.

```

fullAdd (carryIn, (a, b)) = (sum, carryOut)

where

(sum1, carry1) = halfAdd (a, b)

(sum, carry2) = halfAdd (carryIn, sum1)

carryOut = xor2 (carry2, carry1)

```

Note that, just like the half adder, this circuit has *one* input. This one input consists of a pair of a bit and a pair of bits. We could also have represented the input as a triple of bits, but we shall later see why we made this particular choice.

We transcribe the diagram of the circuit (Figure 2.2) by giving names to all the internal signals (here sum1, carry1 and carry2) and then simply writing down all the sub-parts of the circuit. To ease this process, we have decided to read the inputs to a sub-component from bottom to top. The order of the resulting equations doesn't matter. The equations can make use either of previously defined components (such as halfAdd) or of the Boolean gates.

We can simulate this circuit by using the simulate operation that we used in the previous section. Though as inputs get bigger, typing in different test inputs in the interpreter is a lot of work. To avoid this, we can describe a number of test cases in the file First.hs:

test1 = simulate halfAdd (low,low)

test2 = simulate fullAdd (low,(high,low))

test3 = simulate fullAdd (high,(low,high))

And we can perform tests in the interpreter.

Main> test3 (low, high) Main> test2 (high, low)

Note that if we try to simulate a circuit with inputs of the wrong type, we get a type error:

Signal Bool is the type of a single bit wire in Lava.

To simulate your circuit for more than one input at a time, you can use the operation simulateSeq. It takes a circuit and a list of sample inputs as a parameter. Lists are denoted between square brackets.

Main> simulateSeq halfAdd [(low,low), (low,high), (high,low)]

[(low,low), (high,low), (high,low)]

There is a special list, called domain, which contains all the values of a certain input shape.

Main> simulateSeq halfAdd domain

[(low,low), (high,low), (high,low), (low,high)]

Here, domain produced each possible two bit input. To check what those values were, we can simply ask for the value of domain at the appropriate type:

Main> domain::[(Signal Bool, Signal Bool)]

[(low, low), (low, high), (high, low), (high, high)]

Main> domain::[(Signal Bool, (Signal Bool, Signal Bool))]

[(low, (low, low)), (low, (low, high)), (low, (high, low)), (low, (high, high)),

(high, (low, low)), (high, (low, high)), (high, (high, low)), (high, (high, high))]

It is also possible to ask for the type of a given function:

Main> :t halfAdd halfAdd :: (Signal Bool,Signal Bool) -> (Signal Bool,Signal Bool)

Not all input shapes (for example inputs containing numbers!) have a finite domain list associated with them.

#### 2.4 Generating VHDL

Given a Lava circuit description, we can generate VHDL from it, by using the operation writeVhdl. It takes two arguments, the name of the VHDL definition as a string, and the circuit.

Main> writeVhdl "fullAdd" fullAdd Writing to file "fullAdd.vhd" ... Done.

The VHDL file that is generated will assume that there are definitions of the gates. The Lava distribution provides these definitions in the file Lava2000/Auxiliary/lava.vhd. We must load this file into the VHDL working library and compile it.

Normally, the VHDL generator gives names to the inputs and outputs automatically. If we want to give names to the input ourselves, we can do this by using the operation writeVhdlInput. Here is how we use it:

Main> writeVhdlInput "fullAdd" fullAdd (var "carryIn", (var "a", var "b")) Writing to file "fullAdd.vhd" ... Done.

And lastly, if we also want to give names for the outputs, we can use the operations writeVhdlInputOutput. Here is how we use it:

See figure 2.3 for the result of this last operation. Note that the description has been *flattened* all the way down to a gate-level netlist. No hierarchy remains. Lava really is just some modules that help with writing netlist generators. What happens under the hood is that we run the circuit description with symbolic inputs, producing an internal representation of the netlist. Then, we walk over this to print VHDL. Later, we will instead print the netlist in CNF (for input to a SAT-solver) or in SMV input format (for input to a model checker).

Looking at this VHDL code, you can see that it is odd, in that it passes the clock to every combinational gate! If you don't feel like doing this, you -- Generated by Lava 2000

use work.all; entity fullAdd is port -- clock ( clk : in bit -- inputs ; carryIn : in bit

; a : in bit ; b : in bit

-- outputs ; sum : out bit ; carryOut : out bit ); end entity fullAdd;

architecture structural

```

of

fullAdd

is

signal w1 : bit;

signal w2 : bit;

signal w3 : bit;

signal w4 : bit;

signal w5 : bit;

signal w6 : bit;

signal w7 : bit;

signal w8 : bit;

begin

port map (clk, carryIn, w2);

-

c w2

entity id

port map (clk, a, w4);

c_w4

: entity id

: entity id

port map (clk, b, w5);

c w5

c_w3

entity xor2 port map (clk, w4, w5, w3);

c_w1

entity xor2 port map (clk, w2, w3, w1);

c_w7

: entity and 2 port map (clk, w2, w3, w7);

c_w8

: entity and 2 port map (clk, w4, w5, w8);

c_w6

: entity xor2 port map (clk, w7, w8, w6);

-- naming outputs

```

c\_sum : entity id port map (clk, w1, sum); c\_carryOut : entity id port map (clk, w6, carryOut); end structural;

Figure 2.3: The VHDL code for the full adder in fullAdd.vhd.

could use the module VhdlNew and the accompanying gate definitions available in the file gates.vhd in directory Lava2000/Auxiliary. Now, each of the VHDL generation functions has a clocked and unclocked version (writeVHdlClk, writeVhdlNoClk etc.). You should import the module VhdlNew if you want to use these functions. (It has been assumed that your project directory is called work.) The full adder is a purely combinational dircuit, so it makes sense to produce a dircuit without a clock. (We will return to clocks, D flip-flops etc. in a later chapter.) The following example

produces the VHDL code in Figure 2.4

#### 2.5 Exercises

2.1 Define the circuits swap and copy. Swap gets a pair of inputs, and outputs them in the swapped order. Copy gets one input and outputs it twice, as a pair. Here is how they should behave:

Main> simulateSeq swap [(low, high), (low, low), (high, low)]

[(high, low), (low, low), (low, high)]

Main> simulateSeq copy [low, high]

[(low, low), (high, high)]

- 2.2 Define a *two-bit sorter*. It takes as input a pair of bits, and outputs the same bits, but the lowest one on the left hand side, and the highest one on the right hand side.

- 2.3 Define a circuit with no inputs, and one output, which is always high. Hint: input consisting of no wires is written as ().

- 2.4 Define and simulate a *multiplexer* in Lava. A multiplexer circuit has as an input a pair of a signal and a pair (x, y). The output is equal to x if the signal is low, and to y if the signal is high.

- 2.5 Use three full adders to make a three bit binary adder. Simulate your design and generate VHDL code.

- 2.6 Suppose you are designing a digital watch. It might come in handy to have a circuit that takes a four-bit binary number and displays it as a digital digit, using a seven segment display. Your circuit might have the following interface (see figure 2.5):

```

digitalDisplay (one, two, four, eight) =

(a, b, c, d, e, f, g)

where ...

```

12

#### library ieee;

use ieee.std\_logic\_1164.all;

entity fullAddNew is port (

cin : in std\_logic

; a : in std\_logic

; b : in std\_logic

; sum : out std\_logic ; cout : out std\_logic );

end fullAddNew;

architecture structural of fullAddNew is signal w1 : std\_logic; signal w2 : std\_logic; signal w3 : std logic: signal w4 : std\_logic; signal w5 : std\_logic; signal w6 : std\_logic; signal w7 : std\_logic; signal w8 : std\_logic; begin c\_w2 : entity work.wire port map (cin, w2); entity work wire port map (a, w4); c\_w4 c\_w5 entity work.wire port map (b, w5); entity work worg port map (w4, w5, w3); c\_w3 : entity work word port map (w2, w3, w1); c\_w1 : entity work and G port map (w2, w3, w7); c w7 entity work and G port map (w4, w5, w8); c w8 c ¥6 : entity work xorG port map (w7, w8, w6); c\_sum : entity work.wire port map (w1, sum);

c\_cout : entity work.wire port map (w6, cout); end structural;

Figure 2.4: The VHDL code produced by test1 for the full adder.

#### Figure 2.5: Digital display.

Hint: start by making a table with 10 entries (0 ... 9) where you can see what parts of the display should light up for what number.

## Chapter 3

# **Bigger Circuits**

In this chapter we describe how to make more complicated circuits using recursion and *connection patterns*. We will also see how we use numbers in Lava.

#### 3.1 Recursion over Lists

A bit adder takes a pair of inputs. The first part is a carry bit, the second part is a binary number, represented as a list of bits, *least significant bit first*. The bit adder will add the bit to the binary number, resulting in a binary number and a carry out.

We define a bit adder bitAdder in Lava by recursion over the list of bits. There are two cases. Either the list is empty, denoted as [], and there is nothing to add. Or the list has at least one element a, and we can split the list up in two parts, a, the least significant bit, and as, the remaining bits, written a:as. In this case, we will use a half adder to add a and the carry, and *recursively* add the resulting carry to the rest of the binary number.

bitAdder (carryIn, []) = ([], carryIn)

bitAdder (carryIn, a:as) = (sum:sums, carryOut)

where

(sum, carry) = halfAdd (carryIn, a)

(sums, carryOut) = bitAdder (carry, as)

A more complicated circuit is the circuit **adder** that takes a carry and a pair of binary numbers, and adds them up. This is called a binary adder. The recursive structure is almost the same, but we are doing *simultaneous* recursion over both binary numbers.

adder (carryIn, ([], [])) = ([], carryIn)

adder (carryIn, (a:as, b:bs)) = (sum:sums, carryOut)

where

(sum, carry) = fullAdd (carryIn, (a, b))

(sums, carryOut) = adder (carry, (as, bs))

[Note: This adder is actually predefined in the module Arithmetic.]

#### 3.1.1 Generating VHDL for a binary adder

To generate a VHDL netlist for the adder that we have just defined, we need to specify the *size* of the circuit, that we need to fix the lengths of its input lists. This is because we have written a *generic* circuit description using pattern matching over lists, but a netlist must have a fixed size. For example, to fix the lengths of the two binary numbers to be added to 4, we write

test2 = writeVhdlInputOutputNoClk "adder" adder (var "cin", (varList 4 "a", varList 4 "b")) (varList 4 "sum", var "cout")

Typing test2 at the Lava prompt then produces the VHDL file shown in Figure 3.1. It is also possible to parameterise the definition with the adder size:

making it very easy to produce large netlists.

#### **3.2** Connection Patterns

Looking at the two circuit definitions in the previous section, bitAdder and adder, we can see that they have a lot in common. Even though the *gates* that they use are different, their *structure* is very similar.

In Lava, we can capture these common structures in *connection patterns*. Connection patterns are higher-order functions that build circuits from other (smaller) circuits.

A very common connection pattern is the *serial* composition *serial* of two circuits (see figure 3.2). It is a circuit *parametrized* by two circuits circ1 and circ2. This means that *serial* circ1 circ2 is a circuit, which feeds its input a to circ1, connects the output b of it to the input of circ2, and results in that output c.

use ieee.std\_logic\_1164.all; entity adder is port cin : in std\_logic ; a\_0 : in std\_logic ; a\_1 : in std\_logic ; a\_2 : in std\_logic ; a\_3 : in std\_logic ; b\_0 : in std\_logic ; b\_1 : in std\_logic ; b\_2 : in std\_logic : b 3 : in std logic ; sum\_0 : out std\_logic : sum 1 : out std logic ; sum\_2 : out std\_logic ; sum\_3 : out std\_logic ; cout : out std\_logic ): end adder; architecture structural of adder is signal w1 : std\_logic; signal w2 : std\_logic; signal w3 : std\_logic; signal w4 : std logic: signal w5 : std logic: signal w6 : std\_logic; signal w7 : std\_logic; signal w8 : std logic: signal w9 : std\_logic; signal w10 : std\_logic; signal w11 : std\_logic; signal w28 : std\_logic; signal w29 : std\_logic; begin c\_w2 entity work.wire port map (cin, w2); entity work wire port map (a\_0, w4); c\_w4 c\_w29 : entity work.andG port map (w21, w24, w29); : entity work.xorG port map (w28, w29, w27); c w27 c\_sum\_0 : entity work.wire port map (w1, sum\_0); c sum 1 : entity work wire port map (w6, sum\_1); c sum 2 : entity work.wire port map (w13, sum\_2); : entity work wire port map (w20, sum\_3); c\_sum\_3

library ieee;

c cout

end structural;

Figure 3.1: The VHDL code produced for a 4-bit adder (with parts omitted for brevity).

: entity work.wire port map (w27, cout);

Figure 3.2: Serial composition of circ1 and circ2.

serial circ1 circ2 a = c

where

b = circ1 a

c = circ2 b

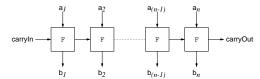

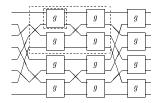

More interesting connection patterns become possible when we consider recursive circuit structures. For example, instead of the half adder circuit in the addBit definition, we can plug in any other circuit. The result consists of a *row* of smaller circuits (see figure 3.3).

Here is how we define the row connection pattern.

row circ (carryIn, []) = ([], carryIn)

row circ (carryIn, a:as) = (b:bs, carryOut)

where

(b, carry) = circ (carryIn, a)

(bs, carryOut) = row circ (carry, as)

Once we have made this definition, we do not need to use recursion anymore to define circuits of this specific pattern. Note that the definition of **row** assumes that the component, **circ**, has a pair as input and produces a pair as output. This was why we chose the type of **fullAd** also to be of this form. Also, if the components are to fit together properly into a linear array, it is necessary that it be possible to connect the second output of one component to the first input of the next. However, the types are not constrained any further than this. Note also that **row** itself also produces a "pair-to-pair" circuit, as does the related connection pattern *column* (see exercises 3.9 and 3.10).

Here are alternative definitions of bitAdder and adder:

bitAdder' (carry, inps) = row halfAdd (carry, inps)

adder' (carry, inps) = row fullAdd (carry, inps)

It turns out that one can get quite far with surprisingly few connection patterns. The module Lava2000/Modules/Patterns.hs contains a few useful patterns (including row). Using these patterns can lead to very concise circuit descriptions that are still easy to read for those familiar with the patterns. It is also convenient to mix the "named wire" style, which we saw in the recursive definitions earlier, with the use of connection patterns.

Even shorter definitions of the same circuits are:

bitAdder' = row halfAdd

adder' = row fullAdd

Note that the type of adder' is slightly different from adder, see exercise 3.3.

#### 3.3 Arithmetic

In Lava, we can not only deal with low-level wire types like bits, and gates like and2 and xor2, but also with more abstract wire types and gates. One of these types is integers (and indeed the lowest level wires in our circuits carry either bits or integers).

On these integers, we have operations corresponding to abstract gates over integers. A list of these gates can be found in appendix A.

A simple circuit using these arithmetic gates is called numBreak. It takes a number as input, and has a pair of a bit and a number as output. The bit in the pair corresponds to the value of the first binary digit of the number; the resulting number is the input number divided by 2.

numBreak num = (bit, num')

where

digit = imod (num, 2)

bit = int2bit digit

num' = idiv (num, 2)

The circuit i2b converts a number into a bit, by transforming a 0 into low, and any other number into high.

We can use this arithmetical circuit to build a circuit that converts a number into a binary number, that is, a list of bits. The circuit takes a parameter, corresponding to the size of the list it has to produce, and has as input the number that needs to be converted.

The converter int2bin converts an integer to a binary number. It has an extra *parameter*, which specifies the number of bits the binary number should have. Note again that parameters of circuits are different from inputs; int2bin is not

really a circuit, but int 2bin 16 is. We define this circuit by recursion over the size of the binary number.

```

int2bin 0 num = []

int2bin n num = (bit:bits)

where

(bit,num') = numBreak num

```

```

(bit,num') = numBreak num

bits = int2bin (n-1) num'

```

Here, the actual circuit input is num, which is the kind of integer that flows in a Lava circuit, and so has type Signal Int. Other arithmetic gates include plus, times, etc.

Here are some example simulations of these circuits:

Main> simulate numBreak 7 (high,3)

Main> simulate (int2bin 3) 7 [high, high, high]

Main> simulate plus (3,4) 7

At present, VHDL netlist generation supports only bit level operations. It will give an error if you try to generate VHDL for a circuit that operates on integers. However, the integers can still be useful! For example, you can use them in testing your arithmetic circuits. Let us wrap our binary adder up in suitable conversions:

wrapAdd n (a, b) = out

where

as = int2bin n a

bs = int2bin n b

(ss,c) = adder (low,(as,bs))

out = bin2int (ss ++ [c])

We supply it with two n-bit inputs, which we produce from the integer inputs a and b. For the output, we stick the carry onto the end of the list of sum bits, since that list is *least significant bit first*. This is done by forming the singleton list [c] and appending that list to the end of the list ss. (++ is the Haskell operator that appends two lists.) Having made a single binary number, we convert the result back into an integer. We would then expect the resulting circuit to behave rather like plus, but with a limit on the size of the inputs that it can deal with. Note that we must fix the size of the parameter n in order to get a circuit that can be simulated.

Main> simulate (wrapAdd 4) (3,5) 8 Perhaps you can figure out why we get

Main> simulate (wrapAdd 2) (3,5) 4

#### 3.4 Exercises

- 3.1 Define a bit subtractor, called bitSubber, which takes a bit and a binary number as input, and subtracts the bit from the binary number.

- 3.2 Define a binary adder, called adder2, which does not take in a carry bit, and throws away the resulting carry.

- 3.3 What is the difference between adder and adder '? Hint: look at the types of the inputs.

- 3.4 Define a circuit bin2int, which converts a bit vector into an integer.

- 3.5 Define the circuit zipp, which takes a pair of list as inputs and produces a list of pairs, one by one grouped together.

Main> simulate zipp ([low,high,low],[high,high,low])

[(low,high),(high,high),(low,low)]

Also define the circuit unzipp, which is the inverse of zipp.

3.6 Define the circuit pair, which takes a list as input and produces a list of pairs, with the neighbours grouped together.

Main> simulate pair ([low,high,low,high,high,low])

[(low,high),(low,high),(high,low)]

Also define the circuit unpair, which is the inverse of pair.

- 3.7 Define a connection pattern called **par** which turns two circuits, each taking in one input and having one output, into one circuit taking in a pair of inputs and having a pair of outputs.

- 3.8 Define, using recursion, a binary multiplier. What is the recursive structure?

3.9 Looking at the definition of row, define a connection pattern called column which carries the right part of the input and the left part of the output through.

(\*) Can you define column in terms of row?

3.10 Define a connection pattern called grid, which puts a number of copies of circuits in a matrix. The left parts of the inputs are carried through from left to right, and the right parts of the inputs and outputs are carried through from top to bottom.

Hint: think of a grid as a row of columns (or a column of rows).

- 3.11 Can you think of a useful circuit that makes use of the grid connection pattern?

- 3.12 Looking at the recursive definition of an adder, define a simple subtractor. It will only have to subtract smaller numbers from bigger numbers. Can you use any of the connection patterns described in this chapter to make a non-recursive description?

- 3.13 Define a swapper, a circuit that takes in two inputs: an activate signal and a pair of signals, and the output is a pair of signals. If the activate signal is high, the order of the input pair is swapped, otherwise is stays the same.

swapper (swap, (a, b)) = (x, y)

where ...

- 3.14 Define a comparator, a circuit that takes in two binary numbers of equal length and tells you if the left one is less than or equal than the right one.

- 3.15 Implement a binary sorter. It takes as an input two binary numbers of equal length, and outputs them in the correct order.

## Chapter 4

# Verification

In this chapter we describe how we can define properties of circuits, and how we can formally verify these properties using a theorem prover.

### 4.1 Simple Properties

The main kind of properties of circuits we deal with in Lava are so-called *safety* properties. These are properties which can be defined in such a way that they state that some condition is *always* true (or, equivalently, never false).

Here is an example; a property that checks that the outputs of a half adder are never both true.

```

prop_HalfAddOutputNeverBothTrue (a, b) = ok

where

(sum, carry) = halfAdd (a, b)

ok = nand2 (sum, carry)

```

Note that this property looks pretty much like a normal circuit definition, and in fact it is.

The actual verification question is: does this property circuit always yield true, no matter what the input is? To answer the question, we use the Lava operation verify.

Main> verify prop\_HalfAddOutputNeverBothTrue Proving: ... Valid.

This process works in the following way. Just as we can generate VHDL from a circuit description, we can also generate a logical formula representing the circuit. This logical formula is then given to an external theorem prover which will prove (or disprove) the validity of the formula. The result is then taken back into Lava.

Here is another example; we formulate that a full adder does not care about the order of the arguments, it will always produce the same result. This property is in general called *commutativity*.

```

prop_FullAddCommutative (c, (a, b)) = ok

where

out1 = fullAdd (c, (a, b))

out2 = fullAdd (c, (b, a))

ok = out1 <==> out2

```

Note that, since we are not interested in the exact shape of the output of the two full adders, we can just give a name to the whole output, in this case out1 and out2. Another thing to notice is that we use the general equality <==>. We can also use the circuit equal for that.

### 4.2 Quantification

The commutativity property is not only true for full adders, but also in general for binary adders. Here is how we state that property:

```

prop_AdderCommutative (as, bs) = ok

where

out1 = adder2 (as, bs)

out2 = adder2 (bs, as)

ok = out1 <=> out2

```

Note that we use the adder adder 2 we defined in exercise 3.2 (the answer is on page 85).

The problem is that this property holds for *all* circuit sizes, but we can only verify it for specific sizes! This is because it is very hard to verify properties automatically for all sizes.

So, instead of verifying it for all sizes, we will pick a specific size and verify the property for those. Thus, we define a new property, which is explicit about what size of input we want to verify the property.

```

prop_AdderCommutative_ForSize n =

forAll (list n) $ \as ->

forAll (list n) $ \bs ->

prop_AdderCommutative (as, bs)

```

This property means: "for all lists of size n called **as**, and for all lists of size n called **bs**, the property that the adder is commutative holds for (**as**, **bs**) as input".

Now, we can verify the property using **verify**. We can of course do this for more than one size.

Main> verify (prop\_AdderCommutative\_ForSize 2) Proving: ... Valid.

Main> verify (prop\_AdderCommutative\_ForSize 4) Proving: ... Valid.

Main> verify (prop\_AdderCommutative\_ForSize 32) Proving: ... Valid.

#### 4.3 General Properties

General properties are properties that are parametrized by one or more circuits. They can be defined just like connection patterns. Here is a general property that poses the question if the two given circuits are equivalent.

prop\_Equivalent circ1 circ2 a = ok

where

out1 = circ1 a

out2 = circ2 a

ok = out1 <==> out2

The following property checks if a given circuit is commutative.

```

prop_Commutative circ (as, bs) = ok

where

out1 = circ (as, bs)

out2 = circ (bs, as)

ok = out1 <==> out2

```

Of course, the circuits that one uses to instantiate these properties have to be of the right shape (type).

#### 4.4 Helping Verification

The formulas that we generate can sometimes be quite hard. It is often the case that, the larger the formula, the harder it is to verify it. So sometimes, it is necessary to help the prover a bit.

One way of doing this is to split up a large proof into a number of smaller ones. Then, we can prove these parts one by one, and for each new proof, we can assume that the parts that are already proved are actually true. In Lava, we can do this by verifying not just *one* question, but a whole list of questions. For example, to verify that two circuits have the same output, we can prove this pin-by-pin instead of at one go. To do this, we have to define *one-by-one equality*.

equalOneByOne ([], []) = [] equalOneByOne ([], y:ys) = [low] equalOneByOne (x:xs, []) = [low] equalOneByOne (x:xs, y:ys) = eq : eqs where eq = equal (x, y) eqs = equalOneByOne (xs, ys)

Note that the comparison fails if the lists are not of the same length. To check that a binary adder is commutative, we can now instead say:

prop\_AdderCommutative' (as, bs) = oks

where

out1 = adder2 (as, bs)

out2 = adder2 (bs, as)

oks = equalOneByOne (out1, out2)

prop\_AdderCommutative\_ForSize' n =

forAll (list n) \$ \as ->

forAll (list n) \$ \as -> forAll (list n) \$ \bs -> prop\_AdderCommutative' (as, bs)

Now we have defined a property that poses a list of questions, we can use the theorem prover to prove all of them.

Lava> verify (prop\_AdderCommutative\_ForSize' 4) Proving: pin 1 ... Valid. Proving: pin 2 ... Valid. Proving: pin 3 ... Valid. Proving: pin 4 ... Valid. Proving: pin 5 ... Valid. --Result: Valid.

Note that in the proof for pin 2, we can assume that pin 1 holds, etc.

26

#### 4.5 Exercises

- 4.1 Take a look at the two bit sorter you defined in exercise 2.2. To verify that it is correct, two properties need to be true:

- The left part of the output is smaller than the right part of the output,

- The output of the circuit contains the same bits as the input (but possibly in a different order).

State these two properties separately, and verify them using verify.

- 4.2 Some properties are so easy to verify that we can actually do it by simulating them for all inputs (using domain). There are a few of these properties in this chapter. Verify them by testing them for all inputs. Can you think of other such easy-to-verify properties?

- 4.3 Check that the various adders in the previous chapter are all commutative, for sizes up to 16 bits. What happens if you try to prove that the subtractor is commutative?

- 4.4 Check that the subtractor you defined in the previous chapter is really a subtractor. How do you formulate your property; what is the "definition" of subtraction? Make sure you do not mess up the sizes of the binary numbers.

- 4.5 Define a general property that states that a given circuit is associative. An operator  $\circ$  is associative, if for every x, y, z it holds that  $(x \circ y) \circ z = x \circ (y \circ z)$ . Are all the adders associative?

- 4.6 Verify that the carry-save adder you defined in the previous chapter is equivalent to a binary adder. Be careful in how you formulate your property, since the inputs do not have the same shape.

- 4.7 Prove that, for an adder and subtractor of your choice, it holds that x + (y-z) = (x+y) z. What extra condition should hold for y and z? How do you express that?

- 4.8 (Haskell) How would you proceed if you want to verify a property for all sizes in between, say, 1 and n?

## Chapter 5

# Sequential Circuits

In this chapter we describe how to deal with sequential circuits in Lava. Sequential circuits in Lava are synchronous circuits, which means that there is one global clock affecting all delay components in the circuit.

#### 5.1 The Delay Component

A new component in sequential circuits is the *delay* component. It is a circuit with one parameter (the initial output of the delay) and one input, which becomes its output in the next clock cycle.

Here is an example of a simple circuit called **edge**, that checks if its input has changed with respect to its previous input. It uses a delay component to remember the previous input.

edge inp = change

where

inp' = delay low inp

change = xor2 (inp, inp')

We can simulate a sequential circuit by using the operation simulateSeq. It needs a circuit and a list of inputs. The list of inputs is interpreted as the different inputs at each clock tick.

Main> simulateSeq edge [high, low, low, high]

[high, high, low, high]

Here is another sequential circuit, which is called toggle. It has an internal state, which it outputs, and it takes one input. If the input is high, it changes the state. If not, it stays the same.

toggle change = out

where

out' = delay low out

out = xor2 (change, out')

As we can see, the definition of out' is dependent on out, whose definition is dependent on out'. Thus, there is a loop in the circuit. Loops are not allowed in combinational circuits, since the meaning of such circuits is unclear. But in sequential circuits, they are essential to implement any interesting behavior.

Simulating toggle gives:

Main> simulateSeq toggle [high, low, low, high] [high, high, high, low]

#### 5.2 Multiple Delays

We have seen how we can delay a signal *one* time instant, so that we can refer to the signal's previous value. Sometimes, we want to delay a signal multiple time instances. We can do this by defining a parametrized circuit, called **delay**. It has two parameters, *n*, the number of delays to use, and **init**, the initial values of these delays.

We use recursion over n to define this circuit.

delayN 0 init inp = inp

delayN n init inp = out

where

out = delay init rest

rest = delayN (n-1) init inp

A useful sequential circuit that we can implement using delayN, is called puls. It has no inputs, one output, and one parameter n. Its output is normally low, except on the n-th, 2n-th, 3n-th, ... dock tick, where it outputs high.

We implement the circuit by creating n-1 delay components in a row, initialized by low, ended with one delay component initialized by high.

puls n () = out

where

out = delayN (n-1) low last

last = delay high out

Note that we need to use a loop back here. This implementation is not optimal, in the sense that it uses too many delay components; see exercise 5.6.

Simulating puls 3 gives:

Main> simulateSeq (puls 3) [(), (), (), (), (), (), ()] [low, low, high, low, low, high, low]

#### 5.3 Counters

An n-bit counter is a circuit that outputs an n-bit binary number at every clock tick, starting with 0, and increasing it by 1 every clock tick. We implement this by keeping an internal state, which is a binary number. The circuit takes one parameter, which indicates the number of bits to use, and has no inputs.

```

counter n () = number'

where

number' = delay (zeroList n) number

(number, carryOut) = bitAdder (high, number')

```

We use the function **zeroList**, which creates a list of *n* zeros, denoting the initial value. Note that the delay component not only works for bits, but also for example for pairs of bits and lists (as in this case).

#### Simulating counter gives:

Main> simulateSeq (counter 3) [(), (), ()] [[low, low, low], [high, low, low], [low, high, low]]

A variant on this circuit is the *up-counter*, which takes an input, which indicates if the number should increase or not. In this case, we want the desired increase to take effect immediately, so we output the number *before* we delay it.

```

counterUp n up = number

where

number' = delay (zeroList n) number

(number, carryOut) = bitAdder (up, number')

```

Simulating counter Up gives:

Main> simulateSeq (counterUp 3) [high, low, high] [[high, low, low], [high, low, low], [low, high, low]]

#### 5.4 Sequentialization

In chapter 3, we have seen a combinational binary adder. As an input, it takes two *n*-bit binary numbers, and adds them up. For large *n*, this circuit can get quite large, which means it takes more circuit area and consumes more power, and will need a lower clock frequency to work properly.

30

We can make use of the regularity in the circuit to make a small version of the circuit that however needs several clock cycles to compute the result. If we apply this technique on the binary adder, we obtain a *sequential adder*. It takes one new digit of both binary numbers at each clock cycle. This is sometimes called *bit serial*.

We can implement this by storing the carry as an internal state, so that the current carry-in of the circuit is the previous carry-out.

```

adderSeq (a,b) = sum

where

carryIn = delay low carryOut

(sum,carryOut) = fullAdd (carryIn, (a,b))

```

Simulating adderSeq gives:

Main> simulateSeq adderSeq [(high,low), (high,high), (low,high)]

[high, low, low]

Because we find that many sequential circuits have this structure, we define a *sequential* connection pattern, called **rowSeq** which builds a row of circuits, just like **row**, but interprets the row *over time*.

rowSeq circ inp = out

where

carryIn = delay zero carryOut

(out, carryOut) = circ (carryIn, inp)

Worth noting is that we make use of the generic **delay** and **zero** component here. The structure is exactly the same as in the sequential adder.

Recalling the definition of a binary adder in terms of row, we can repeat it and implement a sequential adder in terms of rowSeq:

adder' = row fullAdd -- combinational adderSeq' = rowSeq fullAdd -- sequential

In this way, using a connection pattern to define a combinational circuit helps us to define the sequential version of the circuit.

#### 5.5 Variations on rowSeq

The sequential row connection pattern is sometimes useful, but certainly not always. If we use it to implement a sequential adder, as we did, we can also use it to add up "infinitely big" binary numbers. The addition never ends, so we can never start over adding two new numbers. Therefore, it is handy to have a connection pattern, called rowSeqReset, which takes one extra input reset. When reset is high, the internal carry state will be reset to zero.

```

rowSeqReset circ (reset,inp) = out

where

carryIn = delay zero carry

carry = mux (reset, (carryOut, zero))

(out, carryOut) = circ (carryIn, inp)

```

We use the standard multiplexer component mux here, which chooses the left or right component of an input pair, depending on if the first incoming signal is low or high, respectively.

Now we can define a resettable sequential adder adderSeqReset as follows:

#### adderSeqReset = rowSeqReset fullAdd

Very often, it is the case that the internal carry state has to be reset periodically, that is, on every n-th, 2n-th, ... clock tick. Therefore, we create a third sequential row variation, which takes a parameter n, which indicates the reset period.

```

rowSeqPeriod n circ inp = out

where

reset = puls n ()

out = rowSeqReset circ (reset, inp)

```

Now we can define a sequential adder  $\mathtt{adderSeqPeriod}$  adding n-bit numbers as follows:

adderSeqPeriod n = rowSeqPeriod n fullAdd

#### 5.6 Exercises

5.1 Define a circuit evenSoFar, which takes one input, and has one output. The output is high if and only if the number of high inputs has been even so far.

Simulate your circuit in Lava and generate VHDL.

- 5.2 Implement a flipFlop circuit, which takes two inputs (set, reset), and has one output. The circuit keeps an internal state, which is set to high when set is high, and set to low when reset is high. The internal state is also the output. You may decide yourself what to do when both inputs are high.

- 32

- 5.3 Implement a clocked delay component delayClk. It has one parameter, the initial state, and it has an extra input clk. Only when clk is high, the output changes to the state and the state changes to the current input.

- 5.4 Define a circuit called **always**, which has one input and one output. The output is high as long as the input stays high. If the input drops to low, then the output stays low forever.

- 5.5 Define three different circuits that output high only on every 6th clock tick (so it happens on the 6th, 12th, 18th, ... etc.). Use 6 delay elements in the first circuit, 5 delay elements in the second, and 3 in the last.

- Is it possible to define this circuit with less than 3 bit-level delay elements?

- 5.6 Define a puls generator puls2 which has a parameter k, and generates a puls every 2<sup>k</sup>-th clock tick. Your design should use a minimal number of delay components (how many is that?).

- 5.7 Define an up-down counter. The counter gets a pair of inputs. If the left input is high, it counts up. Otherwise, if the right input is high, it counts down. Otherwise, the state stays the same.

- 5.8 Define a 0-to-9 counter. The counter has no inputs, and a 4-bit number as output. Initially, the output starts at 0, and increments at every clock tick, but after the output 9, it returns to 0.

Connect the display from exercise 2.6 to your counter.

5.9 Define a synchronizer, which has two inputs go1 and go2, and one output go. The output only becomes true when both go1 and go2 have been high in the past or are high now since the last go. .

Here is an example simulation:

Main> simulateSeq synchronize [(low,high),(high,low),(high,high), (high,low),(low,low),(low,high)] [low, high, high, low, high]

5.10 Define a circuit called outputList, which has one parameter, a list of values, no inputs, and one output. The circuit outputs the elements in the parameter list one by one at every clock tick repeatedly. Here is an example simulation:

## Chapter 6

# Sequential Verification

In this chapter we describe how we can verify properties of sequential circuits. We restrict ourselves to sequential safety properties.

### 6.1 Sequential Safety Properties

Let us take a look at how to define properties about sequential circuits. In principle, we can use the same techniques as we did with combinational circuits. Let us take a look at some examples.

Here is how we can compare the two sequential adders from section 5.4.

```

prop_SameAdderSeq inp = ok

where

out1 = adderSeq inp

out2 = adderSeq' inp

ok = out1 <==> out2

```

Here is another example; the composition of edge and toggle from section 5.1 gives the identity circuit. This means that the input is the same as the output.

prop\_ToggleEdgeIdentity inp = ok

where

mid = toggle inp

out = edge mid

ok = out <==> inp

The properties we can describe in this way are called *sequential safety properties*. Recall that safety properties are properties which can be described as a circuit with one output, which should always be true (or never be false) for the property to hold.

Examples of properties which are not safety properties are for example *liveness* properties. These can assert that a certain condition must hold at some point in the future, for example.

### 6.2 Sequential Logic

Apart from the techniques we used to define combinational properties, there are also special techniques we can apply to define sequential properties.

- When we want to refer to values of signals at different time instances, we can use a delay to get access to previous values. But be careful about what initial value you choose for this use of delay.

- When we want a certain property only to be true when a certain condition holds, which does not necessarily hold all the time, we can use logical implication. Implication is implemented by the Lava gate impl, and also by the binary operator ==>.

Here is an example. Suppose we want to define the following property about the toggle circuit: "if the input is high, then the current output is different from the previous output".

The way we define this in Lava is:

```

prop_ToggleTogglesWhenHigh inp = ok

where

out = toggle inp

out' = delay low out

change = xor2 (out, out')

ok = inp ==> change

```

First, we compute the output out from toggle. Then, we use a delay component to get access to the previous output out'. We define the situation change in which these outputs differ. And then we say: "if the input is high, then the outputs differ".

### 6.3 Verification

After defining these properties, we would like to formally verify them. Verification of a sequential property means that we have to prove that the property holds at all times. In Lava, we do this by *induction* over time. It works as follows. Firstly, we have to do the *base case*. proving that the property holds for the *first* time instance. Since looking at just one time instance does not involve time at all, we can use the same techniques as we did in the combinational case.

Then, we do the inductive *step*. We want to prove that *if* the property holds at time *t*, it also holds at time *t*+1. We do this as follows: we create an *arbitrary* time instance by filling the states of the circuits with fresh variables. Then, we run the circuit once on that state, obtaining an output and new state values. Then we assert that the output is true, and run the circuit on the new state values. Finally, we need to prove that the new output is true.

After proving the base case and the inductive step, we have proved our property. Here is what happens in Lava:

Main> verify prop\_ToggleEdgeIdentity

Proving: base 1 ... Valid.

Proving: step 1 ... Valid.

-Result: Valid.

Lava> verify prop\_ToggleTogglesWhenHigh Proving: base 1 ... Valid. Proving: step 1 ... Valid.

Result: Valid.

We give a more detailed explanation of induction in the next section.

#### 6.4 Induction

To perform induction on a Lava property, we convert it to a logical formula relating input 'inp' and old state variables ' ${\sf d}_{\sf Old}$  to output 'ok' and new state variables ' ${\sf q}_{\sf new}$ '. Whenever we use a signal-level delay component in a circuit or property, we introduce one state variable.

In this translation, we also introduce a special input, called 'init', which is true only in the first time instance. So, after we have translated the property, we have a logical formula of the following form:

#### $T(\mathsf{init},\mathsf{inp},\mathsf{q}_{\mathsf{old}},\mathsf{q}_{\mathsf{new}},\mathsf{ok})$

This formula is usually called the transition relation.

A very simple way to prove that the output 'ok' is always true, would be to try proving the following:

$T(\mathsf{init}, \mathsf{inp}, \mathsf{q}_{\mathsf{old}}, \mathsf{q}_{\mathsf{new}}, \mathsf{ok}) \Rightarrow \mathsf{ok} \tag{6.1}$

Unfortunately however, this method does not work very often, because even when the property is always true in any run of the circuit, it might not be true in every possible configuration of the state variables. This is why we use induction.

First, we prove the *base case*, that is: 'ok' is true at the first time instance. In this case, we know that the variable 'init' is true, so we prove:

$$T(\mathbf{true}, \mathsf{inp}, \mathsf{q_{any}}, \mathsf{q_{new}}, \mathsf{ok}) \Rightarrow \mathsf{ok}$$

(6.2)

This is usually easy, since initially, we know the values of the state variables.

Then, we prove the *induction step*, that is: if 'ok' is true at time t, it is also true at time t + 1. So, we are looking at two time instances of the property.

$$\left. \begin{array}{l} T(\operatorname{init}_1, \operatorname{inp}_1, \operatorname{q}_1, \operatorname{q}_2, \operatorname{true}) \\ T(\operatorname{false}, \operatorname{inp}_2, \operatorname{q}_2, \operatorname{q}_3, \operatorname{ok}_2) \end{array} \right\} \Rightarrow \operatorname{ok}_2$$

(6.3)

Note how we connect the different time instances 1 and 2 by reuse of the state variables 'q<sub>2</sub>' as new states in the first time instance and as old states in the second time instance. Also note that we use **false** for the value of 'init' in the second time instance, because we know it is not the initial time instance. And we use **true** for the value of ok in the first time, since we may assume that the induction hypothesis holds.

If we have proven the two formulas 6.2 and 6.3, then we know that 'ok' must be true at all time instances. This is the basic notion of induction.

#### 6.5 Induction With Depth

Unfortunately, the method of induction mentioned in the previous section is not *complete*. This means that there are properties which are true, which cannot be proven by simple induction.

Here is an example: Consider the toggle circuit from section 5.1 and the puls circuit from section 5.2. We might want to verify that these circuits do exactly the opposite if toggle always has a high input, and puls has a period of 2.

prop\_Toggle\_vs\_Puls () = ok

where

out1 = toggle high

out2 = puls 2 ()

ok = inv (out1 <==> out2)

This cannot be proven by normal induction, since the **puls** circuit has two delay components in a row, so it is not enough to look at two time instances at a time.

So, instead, we will look at more time instances in the induction proof. We introduce the concept of *induction with depth* k, which means that the base

Figure 6.1: Base case for induction with depth k.

case proves that the first k steps are okay, and the step case may assume that a sequence of k steps went okay, in order to prove that the k + 1-th step is okay.

Here is the concrete formula for the base case (see also figure 6.1):

$$\left. \begin{array}{c} T(\mathbf{true}, \mathsf{inp}_1, \mathfrak{q}_1, \mathfrak{q}_2, \mathsf{ok}_1) \\ T(\mathbf{false}, \mathsf{inp}_2, \mathfrak{q}_2, \mathfrak{q}_3, \mathsf{ok}_2) \\ \vdots \\ T(\mathbf{false}, \mathsf{inp}_k, \mathfrak{q}_k, \mathfrak{q}_{k+1}, \mathsf{ok}_k) \end{array} \right\} \Rightarrow \mathsf{ok}_1, \mathsf{ok}_2, \ldots, \mathsf{ok}_k$$

(6.4)

Note that we use the same trick of reusing the state variables of consecutive times to line up the time instances. Here is the concrete formula for the step case (see also figure 6.2):

$$\left. \begin{array}{c} T\left(\operatorname{init}_{1}, \operatorname{inp}_{1}, q_{1}, q_{2}, \operatorname{frue}\right) \\ T\left(\operatorname{false}, \operatorname{inp}_{2}, q_{2}, q_{3}, \operatorname{true}\right) \\ \dots \\ T\left(\operatorname{false}, \operatorname{inp}_{k}, q_{k}, q_{k+1}, \operatorname{frue}\right) \\ T\left(\operatorname{false}, \operatorname{inp}_{k+1}, q_{k+2}, \operatorname{ok}_{k+1}\right) \end{array} \right\} \Rightarrow \operatorname{ok}_{k+1}$$

(6.5)

So, for any depth k, if we can prove the formulas 6.4 and 6.5, we have proved that 'ok' holds at every time instance. Note that if we choose k = 1, then we are back to normal induction again.

Here is what happens when we verify prop\_Toggle\_vs\_Puls in Lava:

Main> verify prop\_Toggle\_vs\_Puls Prover: base 1 ... Valid. Prover: step 1 ... Falsifiable. Prover: base 2 ... Valid.

Figure 6.2: Inductive step for induction with depth k.

Prover: step 2 ... Valid.

Result: Valid.

So, the verifier realizes that induction depth 1 is not enough for the step to go through, and increases the induction depth automatically. It will keep increasing the depth until either the base case turns out to be false, or until it manages to prove both the base case and the step case.

If we want to specify a specific depth to do the induction for, we can use the operation verifyWith, which takes an extra list of verify options.

Main> verifyWith [Depth 2] prop\_Toggle\_vs\_Puls Prover: base 2 ... Valid. Prover: step 2 ... Valid. --

Result: Valid.

The operation verify is actually just a short-hand for verifyWith [Depth 1, Increasing]. With the option Depth, one can specify the induction depth. Increasing means that it will keep increasing the depth until it proves or disproves the property.

#### 6.6 Induction With Restricted States

Unfortunately, even induction with depth is not a complete method. This means that there exists properies which are always true, but for which there exists no k such that the property can be proven by induction with depth k.

An example of such a property is to check if a periodic sequential adder of period 2 is equivalent to a resettable adder which we reset every second clock tick.

```

prop_AdderPeriod2 ab = ok

where

sum1 = adderSeqPeriod 2 ab

two = delay low (inv two) -- 010101...

sum2 = adderSeqReset (two, ab)

ok = sum1 <=> sum2

```

Verifying this property results in an infinite loop:

```

Main> verify prop_AdderPeriod2

Prover: base 1 ... Valid.

Prover: step 1 ... Falsifiable.

Prover: base 2 ... Valid.

Prover: step 2 ... Falsifiable.

```

The problem is that there exist a lot of state variable configurations that never occur when we run the circuit, but are logically possible. In some cases, these so-called *unreachable states* mess up the induction proof. Even assuming that the property we want to prove is true for a very large number k of consecutive running steps (like we do in the induction step) is not enough to ensure we are in a reachable state. The reason for this is that we might be running around in the unreachable states in circles for these k steps, so increasing k does not help.

Instead, we will strengthen the induction step by saying that all k+1 states we visit in the formula must be distinct. In this way, we ensure that we are not running around in circles.

The new formula for the inductive step becomes:

$q_1$

$$\left. \begin{array}{c} T(\mathsf{init}_1, \mathsf{inp}_1, \mathsf{q}_1, \mathsf{q}_2, \mathsf{true}) \\ T(\mathsf{false}, \mathsf{inp}_2, \mathsf{q}_2, \mathsf{q}_3, \mathsf{true}) \\ \vdots \\ T(\mathsf{false}, \mathsf{inp}_k, \mathsf{q}_k, \mathsf{q}_{k+1}, \mathsf{true}) \\ T(\mathsf{false}, \mathsf{inp}_{k+1}, \mathsf{q}_{k+2}, \mathsf{ok}_{k+1}) \\ \neq \mathsf{q}_2, \ \mathsf{q}_1 \neq \mathsf{q}_3, \dots, \ \mathsf{q}_{k-1} \neq \mathsf{q}_{k+1}, \ \mathsf{q}_k \neq \mathsf{q}_{k+1} \end{array} \right\} \Rightarrow \mathsf{ok}_{k+1} \qquad (6.6)$$

For this method, proving formulas 6.4 and 6.6 for some k is enough to prove the 'ok' holds at all time instances. Moreover, this is a complete method! This

means that, if the property holds, there is always a k such that we can prove it by induction with depth k with restricted states.

To use induction with restricted states in Lava, we can use the option RestrictStates:

Main> verifyWith [RestrictStates,Increasing] prop\_AdderPeriod2 Proving: base 1 ... Valid. Proving: step 1 ... Falsifiable.

Proving: base 5 ... Valid. Proving: step 5 ... Valid.

Result: Valid.

We needed induction depth 5 for this property. Note that we used the option **Increasing** also, otherwise the verification would have stopped at depth 1.

#### 6.7 Exercises

6.1 Why is simulation not enough to do sequential verification?

- 6.2 Verify that the edge circuit and the circuit evenSoFar from exercise 5.1 always have opposite outputs if fed with the same inputs.

- 6.3 Verify that the three different implementations of a puls generator with period 6 in exercise 5.5 are equivalent. What is the induction depth that is needed?

- 6.4 Verify the obvious relationship between the puls circuit and the puls2 circuit from exercise 5.6, for different values of k. What is the induction depth that is needed?

- 6.5 Verify that the up-part of the up-down counter you defined in exercic 5.7 is equivalent to the up-counter from section 5.3. Do this for different values of n.

- 6.6 Define and verify the following property: "if the input to toggle is the same twice in a row, then the current output is the same as the output two steps ago".

- 6.7 Consider the following general property: "As long as A holds, then B must hold". How would you define such a property? Hint: use the always circuit from 5.4.

- 6.8 Show that doing induction with depth 1 amounts to normal induction.

- 6.9 (\*) Show that doing induction with depth k is *sound*, that is, if we have proven the base case and the inductive step, then we have really proven that the property always holds.

- 6.10 (\*\*) Show that doing induction with depth k and restricted states is sound. You may use the fact that exercise 6.9 holds.

- 6.11 (\*\*) Show that doing induction with depth k and restricted states is complete.

## Chapter 7

# **Time Transformations**

In this chapter, we will see some techniques with which we can compare circuits that operate at different clock rates.

### 7.1 Timing Issues

So far, when we were comparing two circuits, we always assumed that they consumed their inputs and produced their outputs at the same rate. Let us take a look at an example where this is not the case: comparing a sequential adder against a combinational adder.

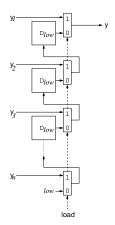

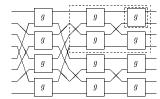

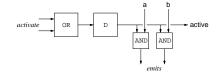

The sequential adder (see figure 7.1) takes in a pair of bits every clock tick, and outputs the sum, and remembers the carry for the next clock cycle. The carry is reset every n-th clock tick. Here is how we defined it:

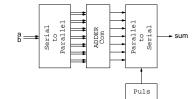

adderSeqPeriod n = rowSeqPeriod n fullAdd

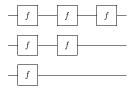

The combinational adder (see figure 7.2) takes in two *n*-bit binary numbers and produces the sum as a *n*-bit binary number in one clock tick. Here is how we define it:

adderCom abs = sum

where

(sum, carryOut) = row fullAdd (low, abs)

Figure 7.1: A sequential adder.

Figure 7.2: A combinational adder.

Figure 7.3: The slowed down combinational adder.

For convenience, we abstract away from the carry.

There are two basic methods for comparing these two circuits.

The first method involves slowing down the combinational adder, so that it takes more clock ticks to calculate the sum. So instead of taking n pairs of bits at a time, it takes them in one-by-one, and when it has gotten all of them, it outputs the sums one-by-one. The circuits now operate at the same rate, and can be compared by conventional methods.

The second method involves speeding up the sequential adder, so that it computes several results in one clock tick. So instead of taking in one pair of bits at a time, it takes in n pairs of bits, and produces n sums in one clock cycle.

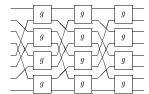

#### 7.2 Slowing Down

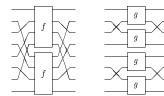

The first technique we describe *slows down* the combinational circuit. So, instead of computing everything in one clock tick, we force it to take n clock ticks instead. We do this by transforming the circuit into a circuit that looks just like the sequential version: it takes one input and produces one output at a time (see figure 7.3).

Since the inputs come in one-by-one, we have to wait for n clock ticks until we have the full input available for the circuit. This is done by the *serial to parallel* converter (see figure 7.4). We can implement this component as follows:

Figure 7.4: A serial to parallel converter.

Figure 7.5: A parallel to serial converter.

serialToParallel 1 inp = [inp]

serialToParallel n inp = inp : rest

where

inp' = delay zero inp

rest = serialToParallel (n-1) inp'

Then we have to take care of the outputs. At every clock tick, the combinational circuit produces n outputs, but they only make sense on every n-th, 2n-th, ... clock tick, because then we have the right input. Therefore, we need to add a component on the outputs that spreads out the outputs of the important clock ticks over the other clock ticks. This is done by the *parallel to serial converter* (see figure 7.5). We can implement this component as follows:

```

parallelToSerial (load, [inp]) = out

where

out = mux (load, (low, inp))

parallelToSerial (load, inp:inps) = out

where

from = parallelToSerial (load, inps)

prev = delay low from

out = mux (load, (prev, inp))

```

Then, we can put these components together in a new sequential adder:

```

adderSlowedDown n ab = sum

where

abs = serialToParallel n ab

sums = adderCom abs

load = puls n ()

sum = parallelToSerial (load, sums)

```

The load input to the parallel to serial converter is a puls with period n. Let us take a look at how this sequential adder adds up binary numbers for n = 4.

| $\operatorname{clock}$ | 1      | 2               | 3               | 4              | 5       | 6       | 7                | 8       | 9      |

|------------------------|--------|-----------------|-----------------|----------------|---------|---------|------------------|---------|--------|

| input                  | $ab_1$ | ab <sub>2</sub> | ab <sub>3</sub> | $ab_4$         | $ab'_1$ | $ab'_2$ | ab' <sub>3</sub> | $ab'_4$ | $ab_1$ |

| output                 | 0      | 0               | 0               | $\mathbf{s}_1$ | $s_2$   | $s_3$   | $\mathbf{s}_4$   | $s'_1$  | $s'_2$ |

As we can see, the results  $s_i$  are delayed by n-1 clock ticks. This is of course because the result is computed at the *n*-th, 2n-th, ... clock tick. So, when we compare this with the original sequential adder, we have to slow the output of that one down with n-1 delay components. Here is the property:

prop\_AdderSeqSlowedDown n ab = ok

where

Figure 7.6: A combinational circuit with explicit states q<sub>old</sub> and q<sub>new</sub>.

Figure 7.7: A time transformed sequential circuit F.

sum1 = adderSeqPeriod n ab sum1' = delayN (n-1) low sum1 sum2 = adderSlowedDown n ab ok = sum1' <==> sum2

Unfortunately, this way of specifying the property introduces a lot of extra logic, and moreover, extra state. This makes the verification of these kind of properties very hard. In particular, the induction methods need an extremely high induction depth. In the next section, we will see a simpler and more direct method for specifying retiming properties.

### 7.3 Speeding Up

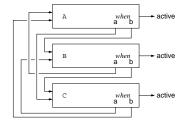

Another technique for retiming works as follows. Instead of slowing down the combinational circuit, we speed up the sequential circuit. Unfortunately, this cannot be done by adding retiming components around the circuit. Instead, we *transform* the circuit into another circuit. This is done by a built-in Lava operation, called timeTransform.

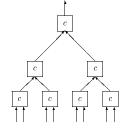

The idea is that we make the state of the sequential circuit explicit by turning a sequential circuit F into a combinational circuit  $F_{expl}$ , that takes in the old state as an extra input, and has the new state as an extra output (see figure 7.6).

The next step is to create a column of  $F_{expl}$ , where we thread the states through as carry. The last step is to make the state implicit again by adding delay components and a loop back (see figure 7.7).

All this is implemented by Lava's primitive operation timeTransform. So, we can make a new adder from the sequential adder, by using time transformation:

adderSpedUp abs = sums

where

sums = timeTransform (adderSeqPeriod n) abs

n = length abs

The function length computes the length of a list, so that we know what period the sequential adder requires.

The property of comparing the two different adders now looks as follows:

prop\_AdderSeqSpedUp abs = ok

where

sum1 = adderSpedUp abs

sum2 = adderCom abs

ok = sum1 <==> sum2

Because this is a property that has a list as an input, we need to be explicit about the length of the list:

prop\_AdderSeqSpedUp\_ForSize n =

forAll (list n) \$ \abs ->

prop\_AdderSeqSpedUp abs

Verifying this by induction is easy, and needs induction depth 2 for any n.

#### 7.4 Exercises

7.1 Consider the following circuit:

highLow () = [high, low]

Verify that the circuit toggle behaves twice as slow as this circuit if its input is always high. Do this by slowing down and speeding up.

7.2 What goes wrong when we try using the slowing down method for comparing two sequential circuits that operate at different rate? Also see exercise 7.5.

Hint: what happens to the state of a circuit that is slowed down?

- 7.3 Does the speeding up method work when we use it for comparing two sequential circuits that operate at different rate?