1

# An Industrially Effective Environment for Formal Hardware Verification

Carl-Johan H. Seger, Robert B. Jones, John W. O'Leary, Tom Melham, Mark D. Aagaard, Clark Barrett, and Don Syme

Abstract—We describe the Forte formal verification environment for datapath-dominated hardware, which has proved effective in large-scale industrial trials. Forte combines an efficient linear-time logic model checking algorithm, symbolic trajectory evaluation, with lightweight theorem proving in higher-order logic. These are tightly integrated in a general-purpose functional programming language, which both allows the system to be easily customized and also serves as a specification language. We also describe the design philosophy behind Forte and elements of the verification methodology that make it effective in practice.

Index Terms—Formal verification, theorem proving, model checking, Symbolic Trajectory Evaluation, BDDs.

#### I. Introduction

UNCTIONAL validation is one of the major challenges in chin design today with chip design today, with conventional approaches to design validation a serious bottleneck in the design flow. Over the past ten years, formal verification [1] has emerged as a complement to simulation and has delivered promising results in trials on industrial-scale designs [2], [3], [4], [5], [6].

Formal equivalence checking is widely deployed to compare the behavior of two models of hardware, each represented as a finite state machine or simply a Boolean expression (often using Binary Decision Diagrams, BDDs [7]). It is typically used in industry to validate the output of a synthesis CAD tool against a 'golden model' expressed in register-transfer level HDL, and in general to check consistency between other adjacent levels in the design flow.

Property checking with a model checker [8], [9], [10], [11] also involves representing a design as a finite state machine, but it has wider capabilities than equivalence checking. Not only can one check that a design behaves the same as another model, one can also check that the hardware possesses certain desirable properties expressed more abstractly in a temporal logic. An example is checking that all requests are eventually acknowledged in a protocol. Model checking is currently much less widely used in practice than equivalence checking.

- C.-J. H. Seger, R. B. Jones, and J. W. O'Leary are at Strategic CAD Labs, Intel Corporation, JF4-211, 2111 NE 25th Avenue, Hillsboro, OR 97124, USA. E-mail: {cseger,rjones,joleary}@ichips.intel.com.

- T. Melham is at Oxford University Computing Laboratory, Wolfson Building, Parks Road, Oxford, OX1 3QD, England. E-mail: Tom.Melham@comlab.ox.ac.uk.

- M. D. Aagaard is at Department of Electrical and Computer Engineering, University of Waterloo, Wateroo, Ontario, N2L 3G1, Canada. E-mail: maagaard@uwaterloo.ca.

- C. Barrett is at Department of Computer Science, Courant Institute of Mathematical Sciences, New York University, 251 Mercer Street, New York, NY 10012, USA. E-mail: barrett@cs.nyu.edu.

- D. Syme is at Microsoft Research, 7 J J Thomson Ave., Cambridge, UK, CB3 0FB. E-mail: dsyme@microsoft.com.

Theorem proving [12], [13] allows higher-level and more abstract properties to be checked. It provides a much more expressive language for stating properties—for example, higherorder logic [14]—and it can deal with infinite-state systems. In particular it allows one to reason with unknowns and parameters, so a general class of designs can be checked—for example, parameterized IP blocks [15]. Industrially, theorem proving is still viewed as very advanced technology and its use is not yet widespread.

BDDs, equivalence checkers, and model checkers all suffer from severe capacity limits. In practice only small fragments of systems can be handled directly with these technologies, and much current research is aimed at extending capacity. Of course it is unrealistic to expect a completely automatic model checking solution. Instead, one needs to find good ways of using human intelligence to extract the maximum potential from model checking algorithms and to decompose problems into appropriate pieces for automated analysis. One approach is to combine model checking and BDD-based methods with theorem proving [16], [17], [18]. The hope is that theorem proving's power and flexibility will enable large problems to be broken down or transformed into tasks a model checker finds tractable. Another approach is to extend the top-level of a model checker with ad-hoc theorem proving rules and procedures [19].

In this paper, we describe a formal verification environment called Forte that combines an efficient linear-time logic model checking algorithm, symbolic trajectory evaluation [20], with lightweight theorem proving in higher-order logic. These are interfaced to and tightly integrated with FL [21], a stronglytyped, higher-order functional programming language. As a general-purpose programming language, FL allows the Forte environment to be customised and large proof efforts to be organized and scripted effectively. FL also serves as an expressive specification language at a level far above the temporal logic primitives.

The Forte environment has proved highly effective in largescale industrial trials on datapath-dominated hardware [3], [22], [23]. The restricted temporal logic of symbolic trajectory evaluation does not, however, limit Forte to pure datapath circuits. Many large 'control' circuits are 'datapath-as-control', and these can also be handled effectively. In addition, the tight connection to higher-order logic and theorem proving provides great flexibility in decomposing verifications into sub-problems that fall into the scope of symbolic trajectory

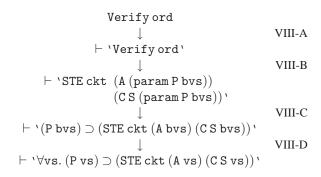

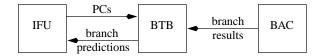

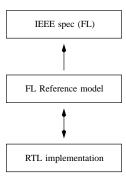

In the next section, we give an account of the design

philosophy behind the Forte environment and describe key aspects of the verification methodology that make it effective in practice. The rest of the paper is then structured as follows. Section III introduces some notation used in the remainder of the paper. Sections IV and V describe symbolic trajectory evaluation ('STE') and some techniques used to scale it up to large circuits. Section VI then explains how the Forte environment embeds STE in the context of the FL programming language. Sections VII and VIII describe how Forte's higher order logic theorem prover is built on FL and how Forte combines STE model checking and deductive theorem proving. Finally, Section IX describes some industrial case studies that illustrate some of the main verification strategies supported by Forte.

The Forte system [24] has recently been made publicly available for non-commercial use. <sup>1</sup>

## II. VERIFICATION AND TOOL DESIGN PHILOSOPHY

There is a large literature on formal proof methods and tools for hardware design verification and debugging. In our experience, this technology is practical only when embedded in a rather sophisticated and finely-tuned environment. All the components deployed—specification languages, model checking algorithms, theorem proving techniques, debugging aids, and so on—must work smoothly together. Substantial engineering effort is needed to move implementations beyond the academic prototype stage typical of most research tools. Additionally, it is critical that the technology be supported by a realistic usage methodology [25], [26].

# A. Formal Specification

The backbone of any verification or design debugging effort is a formal *specification* of required behaviour—or, more loosely, some group of *properties* the design is expected to satisfy, expressed in a formal specification language. We advocate a 'foundational' approach; specifications are expressed in a formalism with only a few very simple temporal logic primitives, but which is also embedded in a full-featured functional programming language. Expressions of the language have a mathematical (logical) interpretation, and so they provide a powerful and extensible layer of specification language on top of the logic primitives.

This approach gives a generic, open framework in which to engineer tailored solutions to individual verification problems. For each verification effort or project, the user can create in the FL functional language just the right specification constructs for the problem domain. In practice, one can reuse much of this over a whole class of verifications, e.g. floating point algorithms. For many verifications suitable FL libraries may already exist, so the tailoring effort can be cost-effective.

By contrast, specialized formal languages are ready for use 'out of the box' but are limited in scope. They can also lead to biases in specifications; just because a branch predictor *can* be written in a notation specialised for some other domain

doesn't mean it's the most natural way to describe branch prediction. The use of FL with temporal logic primitives also gives a specification language that is, in principle, verificationalgorithm neutral and can support abstraction extensions.

Specifications should ideally be concise, implementation-independent, and at a high level of abstraction. Otherwise, there is the danger that specifications are too 'brittle' to track a rapidly-changing design or to be reused on a similar project later on. Small-block verification runs the further danger of reverse engineering meaningless 'specifications' from the circuit itself.

A corollary is that we aim to specify and verify the implementation of *functions*, not to describe and prove correct specific blocks of circuitry. For example, we speak of verifying floating point *instructions* [3], not execution units. A rule of thumb would be to first decompose by function computed and only then structurally (e.g. into pipe stages).

Model checking capacity limits can, of course, compromise the quality of specifications by preventing the verification at the scale needed to implement coherent functionality. Also, optimizing a specification for model checking efficiency can tangle the specification, making the intention less clear. Hence Forte's model checking algorithms and BDD data structures are engineered to scale up to fairly large blocks of hardware.

# B. Debugging in Verification

The bulk of any verification effort is debugging, so it is crucial to optimize the whole verification environment for proof *failure*, not success. We not only want the system to inform us (quickly) when a verification fails; we also want it to provide focused feedback to help us pinpoint the cause of failure. This means a tight, rapid debug loop: simulate (or, later on, verify) the circuit, analyze and debug any counterexample, modify the specification or circuit, and re-simulate.

In practice, most of the bugs are in the verification process itself rather than the device being verified. Early on there will be many bugs in the specification; later, these will become more subtle and harder to distinguish from genuine circuit bugs. An effective environment must supply good machinery for exploring both kinds of bugs, and it must give good feedback in the user's terms from the tools.

Experience has shown that automation and visualization play a large role in providing effective debugging support. It is, of course, essential to be able to both execute specifications and simulate circuits for specific input values to investigate disagreements. Executable specifications are naturally expressible in FL, and simulation is fundamental to symbolic trajectory evaluation. The Forte environment also provides automatic counter-example generation for failed model checking runs, with special care taken about translating internally-generated counter-examples into the user's terms. Additionally, counter-example analysis in Forte is tightly integrated with tools for visualizing circuits and waveforms.

Using a concrete counter-example to isolate the source of a problem is very helpful, but requires the user to understand the behavior of internal signals and do a mental comparison between the circuit and the correct behavior to identify where

<sup>&</sup>lt;sup>1</sup>Available for download at www.intel.com/software/products/opensource/tools1/verification/download.htm.

the circuit fails to meet the specification. It can be much more effective if the user can explore the entire failure domain, or at least intellectually-recognizable subsets of it. For this purpose, Forte provides 'what-if analysis' to help the user understand the failed proofs. The STE model-checking algorithm computes a data structure that gives complete characterization of the difference between the circuit and specification; the user can then invoke FL programs, either drawn from a library or tailor-made for the problem at hand, that probe this data-structure in informative ways.

This facility allows the user to focus on interesting and easily understood counter-examples, instead of being limited to ones chosen arbitrarily by the system. For example, it is often helpful to see a counter-example with as few signals asserted as possible. This can easily be achieved by calling an FL library function that generates a concrete counter-example with this property from the failure domain computed by STE. With a little bespoke FL programming, more domain-specific analyses are also possible. For example, knowing that an arithmetic circuit processes odd numbers correctly but not even ones could focus attention on the least-significant bit, rather than (say) straying into areas of the circuit that compute the sign. One can obtain this information by writing appropriate FL functions to probe the failure domain—in this case discovering that it contains only even numbers.

# C. Reuse of Verification Effort

Verification is an expensive, human-intensive activity. We therefore want to support the reuse of proof efforts to amortize verification cost over the lifetime of a changing design, or even over multiple design projects. Two particularly good targets for reuse are specifications and high-level problem decomposition strategies. These often do not vary greatly from implementation to implementation, and with the right technical machinery they can be insulated from the messy details of individual circuits.

Reuse of specifications depends on having the capacity to treat fairly large-grained functionality, so that specifications can be made as circuit-independent as possible. It must also be possible to structure specifications in a way that separates the circuit-dependent parts and functional parts. In Forte, program structuring in FL is the technology that makes this possible. In practice, of course, achieving a well-structured specification and interface to the circuit needs thoughtful and skilled design. Forte's usage methodology provides some guidance here.

Reuse of problem decomposition strategies depends on making the strategies circuit-independent. A proof based on structural decomposition, or some other implementation feature, is not likely to be reusable for future designs. In particular, model checking routinely handles circuits so large that it is unlikely that one will ever see two identical components whose proofs can be the same.

A better strategy is to base verification methodologies on patterns or common structures in specifications, rather than on patterns in implementations. Specifications are cleaner and generally suffer from fewer idiosyncrasies than circuits. For example, case-splitting strategies derived from analysis of an algorithmically-formulated specification can often be made to transfer across many different circuit implementations.

## D. Usage Methodology

Although continued advances in algorithm and data structure design have increased the reach of formal verification, a large gap remains between the capability offered by verification point-tools and modern design complexity. Much current research targets the well-known problem of model checking capacity limits, but often overlooks the equally important problem of managing the complexity of the verification activity itself. We have therefore coupled our research on technology with work on practical verification *methodology* [25], [26].

Our aim is to make formal verification work at an industrial scale, where any serious verification effort faces many complexity problems in addition to model checking capacity. For example, large verifications are almost always decomposed into many model checking runs—frequently many hundreds. Organizing all the cases to be considered into a coherent whole or even specifying them clearly (let alone discovering them) is complex, intellectually demanding, and error-prone. Our methodology addresses this particular complexity problem by generating and organizing model checking runs systematically.

More generally, the Forte usage methodology gives guiding structure and sequence to the many interdependent and complex activities of a large verification effort. It also helps structure the associated code and proof-script artifacts. The methodology aims, on the one hand, to face the messy realities of design practice (e.g. rapid changes and incomplete specifications) and, on the other hand, to produce high-quality results that are understandable, maintainable—and possibly even reusable.

In related work, Martin *et al.* have developed Versys2, a tool and methodology that uses STE to verify switch-level models of embedded memories against register-transfer-level specifications [27], [28]. By specializing their application to embedded memories, they are able to automate up to 90% of the task of generating specifications and verification scripts. The resulting reduction in verification effort and prerequisite verification expertise enables design engineers to perform most of the verification of embedded memories. In other work, Abadir *et al.* have used the Cycle Based Verilog (CBV) language as the basis for a verification methodology that evolves from formal verification of small blocks to conventional simulation for larger blocks and full-chip verification [29]. In contrast to this work, our aim is to enable industrial-scale formal verification on a wide variety of circuits.

Experience from Forte shows that an effective, broadspectrum verification methodology must meet several key requirements:

*Realism:* An effective verification methodology cannot depend on resources that are not available in the design environment. For example, complete specifications are usually not available, and access to design engineers may be limited.

Transparency and confidence: The verification engineer (and design managers) should clearly know what has been proved and what has not. Of course the methodology and tools should also be sound; false positives should not be possible.

*Structure:* An effective methodology imposes structure on the overall verification effort. This not only helps new users learn, but also increases the productivity of experienced users.

The Forte methodology moves through a series of specific phases, each of which has a specific aim and produces well-defined FL code artifacts [25], [26]. Briefly, the phases are:

- 1) Wiggling (understanding circuit I/O)

- 2) Targeted scalar verification

- 3) Symbolic model checking

- 4) Theorem proving

Having a clear understanding of this sequence gives guiding structure to the work of Forte users. Each phase also produces well-defined code artifacts, which helps to structure verification code. For example, each phase produces an FL function (called a 'test rig') that drives circuit simulation for the purposes of that phase. In each phase, this code evolves from the code of the previous phase by adding some specific new elements. At the completion of a phase, the code is archived for regression.

*Early results:* Preliminary results are needed early in a verification effort. There must be a smooth transition between simulation of special cases and a full proof, so that the effort spent can deliver 'debugging value' very early on.

The simulation-based technology in Forte is especially helpful here. Conventional reachability analysis encounters capacity problems from the very beginning; its goal is to carve out a chunk of circuitry small enough for the capacity of the model checker, but not so small that false counter-examples are generated. In contrast, with symbolic trajectory evaluation and the Forte methodology, one encounters capacity problems gradually. Well before full model checking is attempted, symbolic trajectory evaluation allows debugging with straight simulation or even mixed scalar and symbolic simulation.

Incrementality and regression: If changing a specification, circuit, or library causes a previously-passing proof to fail, it should be possible to use proof artifacts (e.g. test rigs or simulations) from earlier in the effort to help isolate the problem. The methodology's verification artifacts should be easy to maintain and adapt to changing specifications and designs. Test cases from initial proof development should continue to be usable in exploring these changes.

This notion of *incrementality*—always being able to retreat onto solid ground—is especially important when moving into a more advanced phase of work. For example, when a model checking run fails inside a Forte theorem proving proof, it is helpful to be able to 'back off' and execute the model checking run by itself without performing any theorem proving. This makes the debug loop faster, since it is easier to use the debugging facilities tightly integrated with the symbolic trajectory evaluation model checker than operate them through a layer of theorem proving. Likewise, when a symbolic model checking run fails, we can generate a counter-example and then retreat to the simulation domain to analyse it.

Bottom-up and top-down: An effective methodology must support a mix of bottom-up and top-down techniques. The subtle features of designs and the capacity limits of model checking are discovered through bottom-up exploration.

Overall problem reduction is achieved by top-down decomposition, using case splitting, induction, or some other algorithm-specific technique.

The beginning phases of the Forte methodology are primarily bottom-up. This gives early delivery of results and grounds verification in the concrete, transparent world of simulation. One also discovers the (rather unpredictable) limits of model checking by bottom-up exploration, which is much easier than trying somehow to arrive at suitable sub-problems by a top-down decomposition.

The top-down activity of developing case-splits, induction strategies, and other problem reduction strategies—i.e. the high-level proof strategy—starts a bit later, but then proceeds in parallel. This aspect requires an understanding of the algorithm, but the earlier bottom-up explorations help to provide this and to set a definite target for top-down problem reductions to be discovered.

# E. Approach to Technology

Verification by model checking using symbolic trajectory evaluation ('STE') lies at the core of the Forte environment.<sup>2</sup> STE can be viewed as a hybrid between a symbolic simulator and a symbolic model checker [20]. As a traditional simulator, it can compute the result of executing a circuit with concrete Boolean test vectors as inputs; as a *symbolic* simulator, it can also compute symbolic expressions giving outputs as a function of arbitrary inputs. As a model checker, STE can automatically check the validity of a simple temporal logic formula for arbitrary inputs—computing an exact characterization of the region of disagreement in case the formula is not unconditionally satisfied. STE's seamless connection between simulation and verification is crucial to satisfying our requirement for early results.

STE is a particularly efficient model checking algorithm, in part because it has a very restricted temporal logic. But it is well-known that the capacity of any model checker is very limited. To be practical on even small examples, significant engineering effort must be combined with special algorithmic techniques, like partial order reduction [30] or on-the-fly simplification of transition relations [31]. Forte employs a full range of such techniques, but also tackles capacity limits by complementing STE model checking with higher-order logic theorem proving [12], [13].

Theorem proving bridges the gap between big, practicallyimportant verification tasks and tractable model checking problems. From the users' point of view, the Forte philosophy is to have as thin a layer of theorem proving as possible, since using theorem proving technology is still quite difficult. Our experience from case studies is that a surprising amount of added value can be gained from even very simple (mathematically 'shallow') theorem proving.

Architecturally, the Forte approach is to tightly integrate model checking and theorem proving by implementing them within a single framework—the FL programming language

<sup>&</sup>lt;sup>2</sup>Forte also includes a CTL model checker and others, but these will not be discussed in this paper.

and runtime system. A highly engineered and efficient (C-coded) implementation of STE is built into the core of FL, with numerous entry points into STE provided as user-visible FL functions. The Forte theorem prover (called 'ThmTac') is implemented in FL, with an architecture loosely based on the well-tested model of LCF-style proof systems [12].

Two key aspects of this architecture are that it is a 'white-box' integration of model checking and theorem proving and that the FL programming language plays a central role in scripting verification efforts.

1) White-Box Integration: Early efforts in integrating model checkers into theorem provers treated the model checker as a black-box decision procedure that could be invoked in the course of a proof [16], [17]. But experience has shown that a much tighter, white-box integration is far more practical. White box integration means having explicit access to the inner workings of the integrated model checker, for example to analyse or manipulate its internal data structures.

When the model checker is just a decision procedure within a theorem prover, the user can only invoke it to discharge proof obligations. This isolates the user from the powerful debugging and analysis capabilities typically built into model checkers. In addition, practical model checking is rarely, if ever, a simple function that comes back with 'true' or 'false'.

Moreover, if the model checker is a black box with command-line switches, then users learn to convolute their specifications to suit the model checking implementation and become experts at selecting particular flags for particular classes of problems. Verification scripts are then fragile with respect to changes in the specification, circuit, and model checking algorithm. This often leads to precipitous, rather than gradual, degradation when something goes wrong.

Practical model checking involves significant manual interaction, dealing with a variety of issues such as computation of intermediate state sets, installing and analyzing BDD variable orders, and modeling environments. A much more flexible and robust solution is a white-box model checker with a general-purpose programming language as its interface.

2) Proof-Script Programming: A large industrial verification will involve decomposition into many model checking runs—typically several hundred, or even thousands. Clearly some kind of 'verification script' is needed to manage this complex activity, and to form an editable and permanent record of the verification project.

At the very least, a verification script must generate the cases to be checked and control the invocation of individual model checking runs. Assumptions about the operating environment must be formally described (preferably in a user-comprehensible notation) and fed as contraints into the model checking algorithms. It is also essential to be able to check the completeness of coverage. Certainly it should be possible to do this by visual inspection, for example in formal code reviews. But completeness might also be assured by systematically generating the cases to be checked, or even by verifying coverage with theorem proving.

Few model checkers have native scripting capabilities that satisfy these requirements. Existing scripting languages such as Perl or Python are also less than ideal. Perl is best suited for what we might call 'file scripting', controlling essentially stateful actions that must happen in a roughly linear order. But verification scripting is more like the partially-ordered composition of functional operations. Each computation takes some previous results and combines them to produce the next result, and the final outcome is a single piece of data saying that the verification was successful. Moreover, Perl scripts are unsuitable subjects for reasoning about in a theorem prover.

Forte uses the functional language FL to script proof efforts. FL is a full-featured, lazy functional programming language, and so has the advantages of extensibility, semantic cleanness, and perspicuity. It also provides an interface to many of the functions and data structures of STE model checking, so model checking can be highly controlled and easily observed.

But the role of FL in Forte also extends much beyond these basic control and housekeeping functions. As will be seen in later sections, FL provides a specification language for hardware, and it is both the implementation language of the Forte theorem prover as well as the term language for its higher-order logic. FL therefore has a central, unifying role in the Forte architecture.

## III. MATHEMATICAL PRELIMINARIES

We write  $\stackrel{\triangle}{=}$  to mean *equals by definition*. We assume familiarity with elementary propositional logic and predicate calculus notation and use the symbol  $\supset$  for logical implication, reserving the possibly more familiar symbols  $\rightarrow$  and  $\Rightarrow$  for other uses.

We use lower-case letters (e.g.  $a, p_1, v, x, y$ ) for Boolean variables, and upper-case letters (e.g. P, Q) to stand for formulas of propositional logic (i.e. 'Boolean functions'). We write xs to mean a vector of distinct variables  $x_0, x_1, \ldots, x_n$ , for indeterminate n, and Ps to stand for a vector of formulas.

The notation P[Qs/xs] stands for the result of simultaneously substituting the formulas Qs for all occurrences of the Boolean variables xs in P. When the notation P[Qs] is used, it should be understood to represent a term obtainable as the result of such a substitution. Hence P[xs] stands for a logic formula that may contain the variables xs. Normally, P[xs] should simply be taken to mean a formula containing exactly the distinct Boolean variables in xs. In a context in which a formula has been written P[xs], subsequent use of the notation P[Qs] should be understood to mean P[Qs/xs].

We also assume familiarity with the basic notation of naive set theory. (See, for example, [32].) If A and B are sets, we write  $A \rightarrow B$  for the set of all total functions from A to B. We assume that  $\rightarrow$  associates to the right, so  $A \rightarrow (B \rightarrow C)$  may be written  $A \rightarrow B \rightarrow C$ . Function application associates to the left, so if  $f \in A \rightarrow B \rightarrow C$ ,  $a \in A$ , and  $b \in B$ , we can write  $f \ a \ b$  for  $(f \ a) \ b$ .

The semantics of STE depend on some elementary concepts of lattice theory [33]. If  $(S, \sqsubseteq)$  is a partial order and  $A \subseteq S$ , then  $x \in S$  is an *upper bound* for A iff  $a \sqsubseteq x$  for all  $a \in A$ . A *lower bound* is defined dually. An upper bound x of A is the *least upper bound* of A, written lub(A), if  $x \sqsubseteq y$  for every upper bound y of A. The *greatest lower bound*, written glb(A), is defined dually. We write  $a \sqcup b$  (read 'a join b') for  $lub\{a,b\}$

when it exists and  $a \sqcap b$  (read 'a meet b') for  $glb\{a,b\}$  when it exists.

A partial order  $(S, \sqsubseteq)$  is a *complete lattice* iff lub(A) and glb(A) exist for all  $A \subseteq S$ . If S is finite and  $a \sqcup b$  and  $a \sqcap b$  exist for all  $a, b \in S$ , then  $(S, \sqsubseteq)$  is a complete lattice.

## IV. STE MODEL CHECKING

Symbolic trajectory evaluation [20] is an efficient model checking algorithm especially suited to verifying properties of large datapath designs. The most basic form of STE works on a very simple linear-time temporal logic, limited to implications between formulas built from only conjunction and the next-time operator.<sup>3</sup> In addition, STE is based on *ternary simulation* [35], in which the Boolean data domain  $\{0,1\}$  is extended with a third value 'X' that stands for 'either 0 or 1, but we don't know which'. As will be seen later, this gives STE very powerful automatic state-space abstraction.

These characteristics allow STE to perform property checking much more efficiently than conventional model checking algorithms, which operate over more expressive logics like CTL [10]. While the logic of basic STE seems very weak, its expressive power is greatly extended by implementing a *symbolic* ternary simulation algorithm and by being embedded within the FL programming language.

Symbolic ternary simulation [36] uses symbolic Boolean variables and expressions over them (i.e. BDDs [7]) to represent whole classes of data values on circuit nodes. The ternary value associated with each node is represented by a BDD data structure whose variables act as parameters to that value. With this representation, STE can combine many (ternary) simulation runs—one for each assignment of values to the BDD variables—into a single *symbolic* simulation run covering them all.

The BDDs representing values at different circuit nodes can have variables in common, so this representation can also record complex interdependencies among node values. Symbolic values therefore greatly increase the expressive power of the limited temporal logic of STE. For example, input/output relations can be extracted from a circuit by using symbolic simulation to derive BDDs for the values on output nodes as functions of variables standing for arbitrary values on input nodes. These can then be checked against a specification in the form of some reference BDDs.

The expressive power of STE for specifications is also much extended in Forte by embedding the STE logic, including BDD variables, within the FL programming environment. For example, the 'reference BDDs' just mentioned for specifications are typically computed by FL programs, whose source text is the user's view of 'the specification'. Specifications can therefore be expressed clearly and in the user's own terms by using the full expressive power of FL, together with FL library functions especially tuned to describing the problem domain.

The rest of this section explains the background theory of STE model checking in a bit more detail. A full account of the

<sup>3</sup>Extensions of STE to more expressive logics exist [20], [34] and some have implementations in Forte. But this paper will focus on the simplest form, which is also the most widely tested on industrial applications.

theory can be found in [20] and a useful alternative perspective is given in [37].

#### A. Circuit Models

Symbolic trajectory evaluation employs a ternary data model with values drawn from the set  $D = \{0, 1, X\}$ . A partial order relation  $\leq$  is introduced, with  $X \leq 0$  and  $X \leq 1$ :

This orders values by information content: *X* stands for an unknown value and so is ordered below 0 and 1.

We suppose there is a set of *nodes*, N, naming observable points in circuits. A *state* is an instantaneous snapshot of circuit behavior given by assigning a value in D to every circuit node in N. The ordering  $\leq$  on D is extended pointwise to get an ordering  $\sqsubseteq$  on states. We wish this to form a complete lattice, and so introduce a special 'top' state,  $\top$ , and define the set of states S to be  $(N \rightarrow D) \cup \{\top\}$ . The required ordering is then defined for states  $s_1, s_2 \in S$  by

$$s_1 \sqsubseteq s_2 \stackrel{\triangle}{=} \begin{cases} s_2 = \top, \text{ or } \\ s_1, s_2 \in N \rightarrow D \text{ and } s_1(n) \leq s_2(n) \text{ for all } n \in N \end{cases}$$

The intuition is that if  $s_1 \sqsubseteq s_2$ , then  $s_1$  may have 'less information' about node values than  $s_2$ , i.e. it may have Xs in place of some 0s and 1s. If one considers the three-valued 'states'  $s_1$  and  $s_2$  as *constraints* or *predicates* on the actual, i.e. Boolean, state of the hardware, then  $s_1 \sqsubseteq s_2$  means that every Boolean state that satisfies  $s_2$  also satisfies  $s_1$ . We say that  $s_1$  is 'weaker than'  $s_2$ . (Strictly speaking,  $\sqsubseteq$  is reflexive and we really mean 'no stronger than', but it is common to be somewhat inexact and just say 'weaker than'.) The top value  $\top$  represents the unsatisfiable constraint. The *join* operator on pairs of states in the lattice is denoted by ' $\sqcup$ '.

The theory of symbolic trajectory evaluation can in fact be developed for any complete lattice of states [20]. But this generality is not exploited in mainstream implementations of STE, and so we restrict the presentation in this paper to the simple state lattice introduced above.

To model dynamic behavior, a sequence of the values that occur on circuit nodes over time is represented by a function  $\sigma \in \mathbb{N} \rightarrow S$  from time (the natural numbers  $\mathbb{N}$ ) to states. Such a function, called a *sequence*, assigns a value in D to each node at each point in time. For example,  $\sigma$  3 *reset* is the value present on the *reset* node at time 3. We lift the ordering on states pointwise to sequences in the obvious way:

$$\sigma_1 \sqsubseteq \sigma_2 \stackrel{\triangle}{=} \sigma_1(t) \sqsubseteq \sigma_2(t)$$

for all  $t \in \mathbb{N}$

One convenient operation, used later in stating the semantics of STE, is taking the *i*th suffix of a sequence. The *i*th suffix of a sequence  $\sigma$  is written  $\sigma^i$  and defined by

$$\sigma^i t \stackrel{\triangle}{=} \sigma(t+i)$$

for all  $t \in \mathbb{N}$ .

The suffix operation  $\sigma^i$  simply shifts the sequence  $\sigma$  forward i points in time, ignoring the states at the first i time units.

In symbolic trajectory evaluation, the formal model of a circuit c is given by a next-state function  $Y_c \in S \to S$  that maps states to states. Intuitively, the next-state function expresses a constraint on the real, Boolean states into which the circuit may go, given a constraint on the current Boolean state it is in.

A trivial example is this the unit-delay AND-gate, shown together with a partial tabulation of its Y function in Fig. 1. The circuit has three nodes, a, b, and o, and we write a state s as a vector s(a)s(b)s(o). For example s=1X0 means s(a)=1, s(b)=X, and s(o)=0. Reading from the left, we first see that if the inputs a and b are both 1, then the next state is XX1, regardless of whether o is initially 0 or 1. Hence the output o is 1 in the next state and the inputs a and b are both X (i.e. they can be either Boolean value). In fact, the value of o in the next state doesn't depend on the value of o in the current state, so a little further along in the table we also find Y(11X) = XX1.

We also see that if b is 0 in the current state, then the output o is going to be 0 in the next state—regardless of the value of a in the current state. Hence we have Y(X0X) = XX0; we know what the output value will be, even when we have no information about the value on a. Finally, we sometimes have insufficient information to determine the value of the output. If the current state is X1X, for example, then we don't know whether a is going to be 0 or 1—it may be either, and hence Y(10X) = XXX.

In STE, the next-state function for any circuit must be monotonic and a requirement for implementations of STE is that they extract a next-state function that has this property from the circuit under analysis. This condition can be met for a wide variety of common circuit design styles, including synchronous systems with latches as well as flip-flops and systems with gated clocks.

A sequence  $\sigma$  is said to be a *trajectory* of a circuit if it represents a set of behaviors that the circuit could actually exhibit. That is, the set of behaviors that  $\sigma$  represents (i.e. possibly using unknowns) is a subset of the Boolean behaviors that the real circuit can exhibit (where there are no unknowns). For a circuit c, we define the set of all its trajectories, T(c), as follows:

$$T(c) \stackrel{\triangle}{=} \{ \sigma \mid \mathsf{Y}_c(\sigma t) \sqsubseteq \sigma (t+1) \text{ for all } t \in \mathbb{N} \}$$

For a sequence  $\sigma$  to be a trajectory, the result of applying  $Y_c$  to any state must be no more specified (with respect to the  $\sqsubseteq$  ordering) than the state at the next moment of time. This ensures that  $\sigma$  is consistent with the circuit model  $Y_c$ .

## B. Trajectory Evaluation Logic

One of the keys to the efficiency of STE and its success with datapath circuits is its restricted temporal logic. A *trajectory formula* is a simple linear-time temporal logic formula with the following syntax:

$$\begin{array}{rcl} f,g & ::= & n \text{ is } 0 & - \text{ node } n \text{ has value } 0 \\ & | & n \text{ is } 1 & - \text{ node } n \text{ has value } 1 \\ & | & f \text{ and } g & - \text{ conjunction of formulas} \\ & | & P \triangleright f & - f \text{ is asserted only when } P \text{ is true} \\ & | & Nf & - f \text{ holds in the next time step} \end{array}$$

where f and g range over formulas,  $n \in N$  ranges over the nodes of the circuit, and P is a propositional formula over Boolean variables (i.e. a 'Boolean function') called a *guard*.

The basic trajectory formulas 'n is 0' and 'n is 1' say that the circuit node n has value 0 or value 1, respectively. The operator and forms the conjunction of trajectory formulas. The trajectory formula  $P \triangleright f$  weakens the subformula f by requiring it to be satisfied only when the guard f is true. Finally, f says that the trajectory formula f holds in the next point of time.

In essence, a trajectory formula represents a whole *set* of assertions about the presence of the Boolean values 0 and 1 on particular circuit nodes. A guard is a propositional formula that may contain Boolean variables, and a trajectory formula  $P \triangleright f$  with a guard P asserts f only for satisfying assignments of values to the Boolean variables in P. So for any trajectory formula, each assignment of values to the variables in its guards gives a (possibly different) assertion about 0s and 1s on certain circuit nodes at particular points in time.

The various guards that occur in a trajectory formula can have variables in common, so this mechanism gives STE the expressive power needed to represent interdependencies among node values. For example, we can associate an arbitrary propositional formula with a node using the construct 'n is P' defined by

$$n ext{ is } P \stackrel{\triangle}{=} P \triangleright (n ext{ is } 1) ext{ and } \neg P \triangleright (n ext{ is } 0)$$

We can then specify input-output functions using this construct. For example, we might require that if 'in is x' then 'out is F[x]' for some input node in and output node out.

The definition of when a sequence  $\sigma$  satisfies a trajectory formula f is now given. Satisfaction is defined with respect to an assignment  $\phi$  of Boolean truth-values to the variables that appear in the guards of the formula. Following conventional terminology from logic semantics, we call  $\phi$  a *valuation*. We also write  $\phi \models P$  to mean that the propositional formula P is true under the valuation  $\phi$ .

For a given valuation  $\phi$ , we define when a sequence  $\sigma$  satisfies a trajectory formula recursively as follows:

$$\begin{array}{lll} \phi, \sigma \models n \text{ is } 0 & \triangleq & \begin{cases} \sigma(0) = \top, \text{ or } \\ \sigma(0) \in N \to D \text{ and } \sigma \text{ } 0 \text{ } n = 0 \end{cases} \\ \phi, \sigma \models n \text{ is } 1 & \triangleq & \begin{cases} \sigma(0) = \top, \text{ or } \\ \sigma(0) = \top, \text{ or } \end{cases} \\ \phi, \sigma \models f \text{ and } g & \triangleq & \phi, \sigma \models f \text{ and } \phi, \sigma \models g \end{cases} \\ \phi, \sigma \models P \triangleright f & \triangleq & \phi \models P \text{ implies } \phi, \sigma \models f \\ \phi, \sigma \models \mathsf{N} f & \triangleq & \phi, \sigma^1 \models f \end{cases}$$

Note that the same valuation  $\phi$  applies to all the guards that appear in a trajectory formula—so the scope of any Boolean variable is the entire formula. The valuation also does not depend on time.

The key feature of this logic is that for any trajectory formula f and assignment  $\phi$ , there exists a unique weakest sequence that satisfies f. This sequence is called the *defining sequence* for f and is written  $[f]^{\phi}$ . It is defined recursively as follows:

Fig. 1. Simple example of the next-state function

$$[m \text{ is } 0]^{\phi} t \stackrel{\triangle}{=} \lambda n. 0 \text{ if } m = n \text{ and } t = 0, \text{ otherwise X}$$

$[m \text{ is } 1]^{\phi} t \stackrel{\triangle}{=} \lambda n. 1 \text{ if } m = n \text{ and } t = 0, \text{ otherwise X}$

$[f \text{ and } g]^{\phi} t \stackrel{\triangle}{=} ([f]^{\phi} t) \sqcup ([g]^{\phi} t)$

$[P \triangleright f]^{\phi} t \stackrel{\triangle}{=} [f]^{\phi} t \text{ if } \phi \models P, \text{ otherwise } \lambda n. X$

$[Nf]^{\phi} t \stackrel{\triangle}{=} [f]^{\phi} (t-1) \text{ if } t \neq 0, \text{ otherwise } \lambda n. X$

The crucial property enjoyed by this definition is that  $[f]^{\phi}$  is the unique weakest sequence that satisfies f for the given  $\phi$ . That is, for any  $\phi$  and  $\sigma$ ,  $\phi$ ,  $\sigma \models f$  if and only if  $[f]^{\phi} \sqsubseteq \sigma$ .

The algorithm for STE is also concerned with the weakest *trajectory* that satisfies a particular formula. This is the *defining trajectory* for a formula, written  $[\![f]\!]^{\phi}$ . It is defined by the following recursive calculation:

The defining trajectory of a formula f is its defining sequence with the added constraints on state transitions imposed by the circuit, as modeled by the next-state function  $Y_c$ . It can be shown that  $[\![f]\!]^{\phi}$  is the unique weakest trajectory that satisfies f. That is, for any  $\phi$  and  $\sigma$ , we have that  $\sigma \in T(c)$  and  $\phi, \sigma \models f$  if and only if  $[\![f]\!]^{\phi} \sqsubseteq \sigma$ .

As will be seen in the next section, these properties justify using the calculation of defining sequences and defining trajectories as the basis of the STE model checking algorithm.

## C. Model Checking Trajectory Assertions

Circuit correctness in symbolic trajectory evaluation is stated with *trajectory assertions* of the form  $A \Rightarrow C$ , where A and C are trajectory formulas. The intuition is that the *antecedent* A provides stimuli to circuit nodes and the *consequent* C specifies the values expected on circuit nodes as a response.

For example, the AND-gate shown in Fig. 1 would be verified with the following trajectory assertion:

$$\models$$

(a is a) and (b is b)  $\Rightarrow$  (o is  $a \land b$ )

The Boolean variables a and b are used to represent the values on the input nodes and to relate these to the expected value, ' $a \wedge b$ ', on the output node.

A trajectory assertion is true for a given assignment  $\phi$  of Boolean values to the variables in its guards exactly when every trajectory of the circuit that satisfies the antecedent also satisfies the consequent. For a given circuit c, we define  $\phi \models A \Rightarrow C$  to mean that for all  $\sigma \in T(c)$ , if  $\phi, \sigma \models A$  then  $\phi, \sigma \models C$ . The notation  $\models A \Rightarrow C$  means that  $\phi \models A \Rightarrow C$  holds for all  $\phi$ .

The fundamental theorem of trajectory evaluation [20] follows immediately from the previously-stated properties of  $[f]^{\phi}$

and  $[[f]]^{\phi}$ . It states that for any  $\phi$ , the trajectory assertion  $\phi \models A \Rightarrow C$  holds exactly when  $[C]^{\phi} \sqsubseteq [A]^{\phi}$ . The intuition is that the sequence characterizing the consequent must be 'included in' the weakest sequence satisfying the antecedent that is also consistent with the circuit.

This theorem gives a model-checking algorithm for trajectory assertions: to see if  $\phi \models A \Rightarrow C$  holds for a given  $\phi$ , just compute  $[C]^{\phi}$  and  $[A]^{\phi}$  and compare them point-wise for every circuit node and point in time. This works because both A and C will have only a finite number of nested next-time operators N, and so only finite initial segments of the defining trajectory and defining sequence need to be calculated and compared.

In practice, the defining trajectory of A and the defining sequence of C are computed iteratively, and each state is checked against the ordering requirement as it is generated. Each state of the defining trajectory is computed from the previous state by simulation of a netlist description of the circuit over the value domain  $\{0,1,X\}$ .

Symbolic Trajectory Evaluation: The model checking algorithm just sketched requires  $\phi$  to be supplied; given a specific assignment  $\phi$  of values to Boolean variables in the guards of a formula, we can calculate and point-wise compare  $[C]^{\phi}$  and  $[A]^{\phi}$ . But much of the debugging power of STE comes from the key observation that it is not necessary to supply  $\phi$  in advance; instead, the comparison can be computed 'symbolically' to give a *constraint* on  $\phi$ . Such a constraint is called a *residual* and represents precisely the conditions under which the property  $A \Rightarrow C$  is true of the circuit.

This symbolic version of the model checking algorithm works as follows. At the level of basic data values in  $\{0,1,X\}$ , the required computation is to show that

$$[C]^{\phi} t n < [A]^{\phi} t n \tag{1}$$

for all  $t \ge 0$  and  $n \in N$ . For each circuit node at each relevant point in time, we compare the data values expected by the consequent to those given by the circuit and antecedent. To make this comparison 'symbolic', we use a pair of BDDs to encode functions from  $\phi$  to data values in D. This is the so-called 'dual-rail' encoding employed STE implementations [38]. We also extend the simulation algorithm to a symbolic version, in which data values are these pairs of BDDs. The model checking algorithm then compares symbolic states, resulting in the residual.

# D. The STE Deductive System

STE has a sound and complete deductive system for proving trajectory formulas [39], [40], which have been implemented as a set of inference rules in the Forte theorem prover. The complete set of rules is as follows.

- Reflexivity.  $\models A \Rightarrow A$  holds for any trajectory formula A.

- *Time Shift.* For any trajectory formulas *A* and *C*, if  $\models A \Rightarrow C$  then  $\models NA \Rightarrow NC$ .

- Antecedent Strengthening. For any trajectory formulas A and C, if  $\models A \Rightarrow C$  then for any trajectory formula A' for which  $[A]^{\phi} \sqsubseteq [A']^{\phi}$  for all  $\phi$ , we have  $\models A' \Rightarrow C$ .

- Consequent Weakening. For any trajectory formulas A and C, if  $\models A \Rightarrow C$  then for any trajectory formula C' for which  $[C']^{\phi} \sqsubseteq [C]^{\phi}$  for all  $\phi$ , we have  $\models A \Rightarrow C'$ .

- Conjunction. For any trajectory formulas  $A_1$ ,  $A_2$ ,  $C_1$ , and  $C_2$ , if  $\models A_1 \Rightarrow C_1$  and  $\models A_2 \Rightarrow C_2$ , then  $\models A_1$  and  $A_2 \Rightarrow C_1$  and  $C_2$ .

- *Transitivity*. For any trajectory formulas A, B, and C, if  $\models A \Rightarrow B$  and  $\models B \Rightarrow C$ , then  $\models A \Rightarrow C$ .

- Substitution. For any trajectory formulas A and C, if  $\models A \Rightarrow C$ , then  $\models A[Ps/xs] \Rightarrow C[Ps/xs]$  for any substitution of formulas Ps for Boolean variables xs.

The main purpose of these rules is to combine individual STE model-checking results together [41] to derive correctness results that are infeasible to model-check directly. The inference rules can also be used to transform trajectory formulas to increase model checking efficiency [42]. The use of STE inference rules to support these strategies is illustrated by the examples in Section IX.

## V. STE IN PRACTICE

For a given trajectory assertion  $A \Rightarrow C$  and circuit c, STE implementations construct the defining trajectory  $[A]^{\phi}$  incrementally by ternary symbolic simulation of an HDL or a netlist source for the circuit c under the antecedent A. The circuit model  $Y_c$  exists only implicitly in the sequence of simulation states constructed. The number of circuit nodes that can be handled by the symbolic simulator used in this process is essentially unlimited; the limit on the capacity of STE comes from the memory requirements for representing the symbolic values on each node.

Two important optimizations enable STE to be applied to a much larger class of circuits and properties than would otherwise be feasible. *Weakening*, the first of these optimizations, exploits the partially-ordered lattice of STE. The second optimization, the *parametric representation*, takes advantage of the fact that STE is implemented with a symbolic simulator.

Both optimizations can make a big difference to the time and space needed for verification, and can enable verification of circuits that are infeasible to verify directly with STE.

# A. Weakening

Weakening is a data abstraction technique that exploits the partially-ordered state space of STE. It is an implementation optimization, in that it reduces the complexity of the BDDs needed to verify a circuit property.

Recall from the previous section that the definition of a trajectory assertion  $\models A \Rightarrow C$  is  $[C] \sqsubseteq [A]$ , i.e. the defining sequence of the consequent C must be weaker than the defining trajectory of the antecedent A. We say that a node is *weakened* when its value is moved down in the lattice (towards X).

Fig. 2. Dynamic Weakening

Consider the extreme case, when a node's value is replaced with X by modifying the next-state function  $Y_c$ . This means that the node could be either 1 or 0, resulting in a new defining trajectory  $[\![A]\!]_w$  that is 'weaker' than the original defining trajectory  $[\![A]\!]_w$  holds, then from definition of  $\sqsubseteq$  and monotonicity we know that  $[\![C]\!] \sqsubseteq [\![A]\!]_w$  also holds. Note that if the verification fails with the weakened defining trajectory, then we can draw no conclusions about the original trajectory assertion.

Forte provides fine-grained access to weakening by user-level directives that list selected nodes and simulation times at which to weaken them. Users can manually weaken individual nodes at arbitrary points of time during simulation, with a view to reducing the BDD complexity of their values. This is safe, because the theory just sketched tells us that however a node's value is weakened during a verification, if the verification succeeds then the assertion being checked still holds.

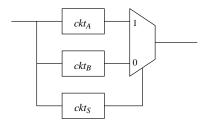

One useful application of weakening is when different parts of a circuit require different BDD variable orderings. Consider the circuit shown in Fig. 2, which selects between the two values computed by  $ckt_A$  and  $ckt_B$  on the basis of a decision made by  $ckt_S$ . Such circuits are common in high-performance pipelines, where multiple speculative results are computed in parallel before knowing which result will be selected.

Suppose that for a particular case of a verification proof, we know that the value produced by the select logic in  $ckt_S$  will be 1. This means that the result of  $ckt_B$  will be 'blocked' at the mux while the result of  $ckt_A$  will be passed to the output. In this case of the proof, the computation done by  $ckt_B$  is irrelevant to the result, but because the nodes of  $ckt_B$  are in the fanin of the output they will not be removed from simulation by automatic cone-of-influence reduction.

If the variable ordering needed for computing the output of  $ckt_A$  is different from that for computing the output of  $ckt_B$ , the BDDs in  $ckt_B$  can explode in size. Because we know from the case split that the value computed by  $ckt_B$  is irrelevant, we would like to prevent its calculation in the first place. This can be accomplished by weakening every input and state node of  $ckt_B$ . If we do this, the output of  $ckt_B$  will be driven X by the circuit, and the BDD explosion will be avoided.

Of course the difficulty with this approach is knowing which nodes to weaken. It is often far from obvious which nodes are *not* involved in a particular computation, and discovering this can involve a very tedious and time-consuming manual effort. Moreover, our wish to support reuse means proof scripts should not be cluttered with implementation-specific information such as node names. This makes the proof scripts

brittle in the face of potential design changes and unsuable on future designs.

Forte therefore supports two other approaches that use weakening in a more automatic fashion. The first, *dynamic weakening*, applies weakening in a rather coarse way and requires little or no user intervention. The second, *symbolic indexing*, uses weakening systematically for verification of regular structures such as memory arrays.

1) Dynamic Weakening: In dynamic weakening, nodes in the circuit are simply weakened when their associated BDDs exceed some size threshold. This occurs dynamically during symbolic simulation and without user intervention. As a result, the weakening takes place without any mention of circuit nodes in proof scripts; the user provides only the size threshold. This works surprisingly well in practice, typically because the nodes with exploding BDDs (e.g. those in  $ckt_B$  above) are exactly the ones that do not have a substantive part to play in the property of interest.

A subtle difficulty remains. Consider the case where the outputs of two sub-circuits are both needed but where the two subcircuits have different variable-ordering requirements. We cannot weaken one of the sub-circuits with Xs because its outputs are necessary for the computation. We address this difficulty by running STE more than once, each time with a different variable order.

Consider again the circuit in Fig. 2. Suppose the the BDD orderings needed for sub-circuits  $ckt_A$  and  $ckt_S$  are different. We first run STE with an ordering for  $ckt_S$  while weakening  $ckt_A$  and  $ckt_B$ . During this STE run, the output of  $ckt_S$  is traced and saved for later use; this process can be repeated as many times as necessary for each sub-circuit that requires a different ordering. For the final STE run, the variable ordering for  $ckt_A$  is used. The results from the earlier run for  $ckt_S$  (and potentially other sub-circuits) are composed with this STE run by strengthening the antecedent with the values traced from the output of  $ckt_S$  that were saved earlier.

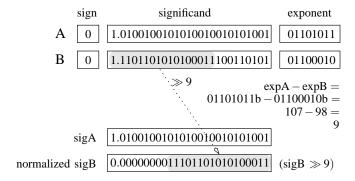

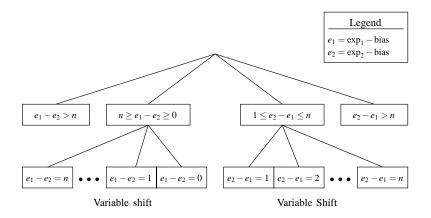

An interesting example where we have encountered this situation is in the verification of floating-point adders. Modern adders use a performance-enhancing 'leading-zero anticipator' (LZA) circuit in subtract mode. The BDD variable order required to reason about LZA circuits is different from the variable orderings required for a variable-shift operation that is internal to the adder. We verified the adder by first running STE with the LZA ordering while tracing the outputs of the LZA sub-circuit. The antecedents for the 'main' STE runs were strengthened with the traced LZA values and performed with the variable orderings required by the core adder circuits. This was significantly easier than explicitly reasoning about the LZA circuitry, as required by other approaches [43].

2) Symbolic indexing: Symbolic indexing is a systematic way of using weakening to perform data abstraction for regular circuit structures. Like dynamic weakening, it is an implementation optimization. However, instead of managing BDD size by driving ternary values towards X, it reduces the number of BDD variables needed to verify certain circuit properties. Intuitively, symbolic indexing is a way to use BDD variables only 'when needed'.

The idea behind symbolic indexing can be illustrated using

the following trivial example. Consider the three-input AND-gate shown below:

With direct use of STE, the assertion we would formulate to verify this device is the following:

$$\models$$

(a is a) and (b is b) and (c is c)  $\Rightarrow$  (o is  $a \land b \land c$ ) (2)

In primitive form, this would be expressed as follows:

$$\models \neg a \rhd (a \text{ is } 0) \text{ and } a \rhd (a \text{ is } 1) \text{ and}$$

$$\neg b \rhd (b \text{ is } 0) \text{ and } b \rhd (b \text{ is } 1) \text{ and}$$

$$\neg c \rhd (c \text{ is } 0) \text{ and } c \rhd (c \text{ is } 1)$$

$$\Rightarrow$$

$$\neg a \lor \neg b \lor \neg c \rhd (o \text{ is } 0) \text{ and } a \land b \land c \rhd (o \text{ is } 1)$$

The strategy here is to place unique and unconstrained BDD variables onto each input node in the device, and symbolically simulate the circuit to check that the desired function of these variables will appear on the output node. The total number of variables needed is the same as the number of input (plus state) nodes, in this case three.

Symbolic indexing exploits STE's partially-ordered state spaces to reduce the number of variables needed to verify a property. In the case of the AND gate, it turns out that we need to verify only the four cases enumerated in the table below:

| case | а | b | С | 0 |

|------|---|---|---|---|

| 0    | 0 | Χ | Χ | 0 |

| 1    | Χ | 0 | Χ | 0 |

| 2    | Χ | Χ | 0 | 0 |

| 3    | 1 | 1 | 1 | 1 |

If all three inputs are 1, then the output is 1 as well. But if at least one of the inputs is 0, the output will be 0 regardless of the values on the other two inputs. In these cases, therefore, we may use the lattice value X to represent the unknown truth-value present on the other two input nodes. As any weakened property implies a stronger property with any substitution of 0 or 1 for the unknown nodes, the four cases we have enumerated cover all possible input patterns of 0s and 1s and are sufficient for a complete verification of the AND-gate.

Symbolic indexing is the technique of introducing Boolean variables to enumerate or 'index' groups of cases like that just described. In the STE assertions (2) and (3) above, the cases we would like to enumerate are represented in terms of the three Boolean variables a, b, and c. Since there are just four cases to check, we can index the cases to be considered with two Boolean variables p and q, as shown below:

| p | q | а | b | С |

|---|---|---|---|---|

| 0 | 0 | 0 | Χ | Χ |

| 0 | 1 | X | 0 | Χ |

| 1 | 0 | Χ | Χ | 0 |

| 1 | 1 | 1 | 1 | 1 |

To verify these cases with STE, we would check the following trajectory assertion:

$$\models \neg p \land \neg q \rhd (a \text{ is } 0) \text{ and } p \land q \rhd (a \text{ is } 1) \text{ and}$$

$$\neg p \land q \rhd (b \text{ is } 0) \text{ and } p \land q \rhd (b \text{ is } 1) \text{ and}$$

$$p \land \neg q \rhd (c \text{ is } 0) \text{ and } p \land q \rhd (c \text{ is } 1) \text{ and}$$

$$\Rightarrow$$

$$\neg p \lor \neg q \rhd (o \text{ is } 0) \text{ and } p \land q \rhd (o \text{ is } 1)$$

If this property is true, the device satisfies the specification of intended behavior for an AND-gate.

Symbolic indexing finds its greatest utility in verification of regular memory structures, as it significantly reduces the number of BDD variables required to encode data values [44], [45], [46]. Consider an  $n \times m$ -bit memory M with n rows and m bits per row, i.e. the memory is accessed with a  $log_2n$ -bit address and returns m bits of data. Suppose we want to verify that the memory correctly stores and returns arbitrary data at every address. We could first perform a write operation to the symbolic address  $a_1$  with the symbolic data vector  $d_1$ . Next, we would perform a read operation of a symbolic address  $a_2$  and check that the result data  $d_2$  matched what we had written previously.

To distinguish between each memory location in the direct verification approach would require  $n \times m$  unique bits: m bits for each of n rows. For even a small memory, the number of variables required is too large for symbolic verification. But suppose we replace the i-th bit in the j-th row with the expression  $P_j[a] \triangleright m_i$ , where  $P_j[a]$  is the appropriate address function for the j-th row. If the address bits select row j, then the value of bit i will be  $m_i$ . If the address bits select a different row, the value of bit i will be X. If we apply the same expression in each row of the memory array, only  $m + \log_2 n$  variables are required: a significant reduction from the  $m \times n$  otherwise needed.

See [47] for further details on symbolic indexing, including an algorithm for transforming directly-stated trajectory assertions, of the kind suitable for higher-level reasoning, into symbolically indexed form for efficient model-checking.

## B. The Parametric Representation

In this section, we begin with a brief explanation of the parametric representation and then describe its use in STE verification. An extended treatment is found in [48].

The goal of the parametric representation is to encode a Boolean predicate P as a vector of Boolean functions whose range is exactly the set of truth assignments satisfying P. The technique is independent of the symbolic simulation algorithm, does not require any modifications to the circuit, can be used to constrain both input and internal signals, and is applicable to a wide variety of circuits.

In a parametric representation, a vector of functions over fresh parametric variables encodes a set of Boolean vectors whose elements are defined by a characteristic function. The range of the functional vector is exactly the original set. To illustrate, consider the following set:

$$S \stackrel{\triangle}{=} \{(1,0,0,1), (1,0,0,0), (0,1,0,1)\}$$

If the input variables for the circuit are expressed as a vector  $as = a_0, a_1, a_2, a_3$  then a non-minimized characteristic function (predicate) for S is:

$$P = (a_0 \land \neg a_1 \land \neg a_2 \land a_3) \lor (a_0 \land \neg a_1 \land \neg a_2 \land \neg a_3) \lor (\neg a_0 \land a_1 \land \neg a_2 \land a_3)$$

The same set can be represented using a parametric functional vector with new *parametric* variables  $p_0$  and  $p_1$  as:

$$Qs = (p_0, \neg p_0, 0, \neg p_0 \lor p_1)$$

Any assignment to the parametric variables yields a truth assignment that satisfies P, as shown in the table below. Note that although (0,1,0,1) appears twice in the table, the range of the parametric function vector is exactly the set S.

| $p_0 p_1$ | value of Qs |

|-----------|-------------|

| 0 0       | (0,1,0,1)   |

| 0 1       | (0,1,0,1)   |

| 1 0       | (1,0,0,0)   |

| 1 1       | (1,0,0,1)   |

The parametric representation is used with a symbolic simulator by applying the vector *Qs* to the inputs in place of the original vector *as*. Each circuit input is replaced with the corresponding function from the vector of parametric functions:

$$\begin{array}{ccc} a_0 & \mapsto & p_0 \\ a_1 & \mapsto & \neg p_0 \\ a_2 & \mapsto & 0 \\ a_3 & \mapsto & \neg p_0 \lor p_3 \end{array}$$

A symbolic simulator can use these functions as inputs without any modification. An algorithm for computing a parametric representation, correctness requirements for the algorithm, and correctness proofs are found in [48]. Similar approaches to the use of parametric encoding are described in [49], where parametrically encoded functional dependencies are used to reduce the complexity of symbolic simulation; and in [50], where parametric representations are used in bounded model checking.

1) Application: Many hardware circuits are designed to function on a defined set of legal inputs and circuit behavior on inputs not in this set does not matter. Additionally, reduction of formal verification complexity is often accomplished by case splitting, dividing the verification into multiple cases that when considered together imply the full verification.

Consider a Boolean predicate P[xs] defined over a vector of variables xs, each of which represents a circuit input or an internal signal at a fixed (but possibly different) point of time. If P[xs] describes an environment constraint or one case of a case split, we need only consider the behavior of the circuit under valuations that satisfy P[xs]. The desired behavior of the circuit will be expressed as an assertion  $\models A[xs] \Rightarrow C[xs]$  over the same variables xs. Because this assertion needs to hold only when P[xs] is true, we wish to establish that P[xs] implies  $\models A[xs] \Rightarrow C[xs]$ . We will express this implication by writing  $P[xs] \models A[xs] \Rightarrow C[xs]$ .

A naive approach would do this verification in three steps:

- 1) Represent the desired restriction as a predicate P[xs].

- 2) Express the specification as a consequent C and compute  $\models A[xs] \Rightarrow C[xs]$  by symbolic circuit simulation.

- 3) Evaluate  $P[xs] \models A[xs] \Rightarrow C[xs]$  by checking that  $\phi \models P[xs]$  implies  $\phi \models A[xs] \Rightarrow C[xs]$  for all  $\phi$ .

This approach has the disadvantage that it evaluates (symbolically simulates)  $\models A[xs] \Rightarrow C[xs]$  for *all* valuations of the variables xs, not just the ones that satisfy P[xs]. But in many cases  $\models A[xs] \Rightarrow C[xs]$  cannot be computed directly with a symbolic simulator because the complexity is too great.

A better approach is to evaluate  $\models A[xs] \Rightarrow C[xs]$  only for valuations that satisfy P[xs]. We do this with a parametric representation that encodes P[xs] as a vector of functions over fresh parametric variables. Suppose the function param computes a parameterized functional vector representation

$$Qs = param(xs, P[xs])$$

Then the implication  $P \models A \Rightarrow C$  we wish to prove becomes a simple trajectory assertion  $\models A[Qs/xs] \Rightarrow C[Qs/xs]$ , in which the original input variables are replaced by the parametric functions.

It is often feasible to compute this encoded trajectory assertion with a symbolic simulator when a direct computation of the trajectory assertion is not possible. The parametric representation is also used in case splitting: each case is characterized by a Boolean predicate that is similarly encoded into the trajectory assertion.

Computing the assertion  $\models A[Qs/xs] \Rightarrow C[Qs/xs]$  is equivalent to checking that P[xs] implies  $\models A[xs] \Rightarrow C[xs]$  for every assignment of values to the variables xs. A proof is provided in [48]. A side condition requires that P[xs] be satisfiable because no functional vector can encode *false*.

It is often the case that symbolic simulation is infeasible even within the restricted domain of P[xs]. Verification complexity can be further reduced by decomposing P[xs] into multiple partitions to represent case splits. In fact, decomposing P[xs] is our primary use of the parametric representation. We illustrate this with the examples in Section IX. Often, different variable orderings are used for different case splits. These orderings can be supplied by the user or, in some cases, determined automatically by the BDD engine.

The strategy of input case-splitting is also the basis of the 'quasi-symbolic simulation' method of Wilson and Dill [51], in which simulation complexity is controlled by representing input cases in an approximate way using constants (called 'symbolic variables') as input values. More generally, simple case-splitting on the two binary values of an input is of course a widespread verification technique.

## VI. THE FL PROGRAMMING LANGUAGE AND STE

FL is a strongly-typed, lazy, functional programming language. Syntactically, it borrows heavily from Edinburgh-ML [12]. Semantically, its core is similar to lazy-ML [52]. A distinguishing feature of FL is that a BDD package is integrated with the language's runtime system, with every

object of the Boolean type bool being represented as a BDD.<sup>4</sup>

The FL language lies at the heart of Forte. Through its embedded BDD package and primitive or defined functional entry-points, it provides a flexible interface for invoking and orchestrating model checking runs. It is also used as an extensible 'macro language' for expressing specifications, which are therefore human-readable but when executed compute efficiently checkable properties in a low-level temporal logic. Finally, it provides the control language for Forte's theorem prover and—through the concept of *lifted FL* [21]—the primitive syntax of its higher order logic.

Trajectory formulas are implemented in FL as lists of *five-tuples*. Each five-tuple specifies an assertion about a single signal and contains the following elements:

- a Boolean guard specifying when the assertion is active

- the name of the signal (a string)

- a Boolean value to assert on the signal

- a start time (integer)

- an end time (integer)

A list of five-tuples represents the conjunction of the individual assertions. The representation of temporal information by intervals (start and end times) is more convenient in practice than the use of a "next time" operator.

The five-tuple representation adds no logical expressiveness. Its major advantage is that it represents formulas using standard data types in FL and similar languages. It is particularly important that the guard and value fields in each five-tuple use FL's BDD representation of Boolean propositions. Users therefore have the complete freedom of a general-purpose functional programming language in which to write both temporal and value properties, facilitating concise and readable specifications.

The orthogonality of the temporal aspect (the two time fields) of the five-tuples from the data computation (the guard and value fields) has a number of positive ramifications. Although trajectory formulas are not generally executable, the individual fields are executable. For example, users can evaluate the data aspect of their specifications simply by evaluating the FL function that computes the intended result. Standard rewrite rules and decision procedures over Booleans can be applied to the guard and data fields. Rewrite rules and decision procedures for integers can be applied to the temporal fields.

Circuits are represented in FL as objects of a special built-in type fsm. An fsm is a directed graph where nodes correspond to gates and edges to connections between gates. Nodes in the graph are annotated with their stimulus functions, delays, and other attributes. A number of built-in functions support structural queries, breadth-first or depth-first traversal, and finding out dynamic information about circuit nodes (e.g. waveforms). This functionality is available through a graphical user interface and as primitive functions in FL, enabling users to program their own custom queries. This has proved extremely valuable for circuit analysis and debugging. Objects of type

<sup>&</sup>lt;sup>4</sup>Strictly speaking, the type of these objects should be something like env → bool, where env is an interpretation of the variables used in the BDD. However, for convenience the global environment is kept implicit and the type abbreviated to bool.

fsm can arise from a number of sources. Translators have been written from Intel's gate-level and schematic-level netlist formats to a special data representation which can then be loaded by FL. Furthermore, primitives available in FL allow the interactive, programmable construction of fsms.

Like the circuit manipulation functions, symbolic trajectory evaluation is available as a primitive function in FL:

$$\mathtt{STE} :: \mathtt{fsm} \to \mathtt{tf} \to \mathtt{tf} \to \mathtt{bool}$$

STE takes three arguments. The first is an fsm. The second and third are an antecedent A and a consequent C, both temporal formulas represented as lists of five-tuples. The result returned is a Boolean formula that is the weakest condition under which  $A \Rightarrow C$  (Section IV).

In our methodology STE is usually invoked in a stylized way.

Here, ckt is the circuit under consideration. The antecedent A captures the protocols and timing required at the circuit inputs, and is an FL function parameterized by vs, a list of symbolic values to use as input data to the circuit. The consequent C formalizes the protocols and timing required at the circuit outputs, and is parameterized by a *functional specification* S as well as the list of symbolic values vs. We call the functions A and C, taken together, a *circuit API*. S serves as a specification of the intended function of the circuit, independent of timing: for a list of symbolic input variables vs, S vs computes the symbolic values expected at the circuit's outputs.

We have developed a wide range of FL functions to ease the task of writing circuit APIs and functional specifications. For example, in capturing input/output protocols it is often convenient to specify event timing relative to a given clock signal, rather than in absolute time ticks. Such a specification style is supported by a library of temporal abstraction and clocking functions. As another example, functional specifications must often model arithmetic and logical computations on bit vectors. Common bit-vector operations are supported by another library of FL functions.