| Title:         | Specification and Verification II     |  |

|----------------|---------------------------------------|--|

| Lecturer:      | Mike Gordon                           |  |

| Class:         | Computer Science Tripos, Part II      |  |

| Term:          | Easter Term 2002                      |  |

| First Lecture: | Friday, 26 April, 2002                |  |

| Location:      | WGB Small Lecture Theatre (Theatre 2) |  |

| Duration:      | Twelve lectures (M. W. F. 12)         |  |

## Specification and Verification II

### Mike Gordon

#### Overview

These lecture notes are for the course entitled Specification and Verification II. The topic of this course is the specification and verification of hardware. Knowledge of the contents of the Part II course on the specification and verification of software entitled Specification and Verification I is assumed.

#### Learning Guide

These notes contain general and background material for the course.

Some of the material in the notes may not be covered in the course, and some additional details and examples are only presented in the lectures.

The examinable material is what is actually covered in the lectures.

#### Acknowledgement

The section entitled *Temporal Abstraction* contains text derived from an early version of the book *Higher Order Logic and Hardware Verification* by Thomas F Melham (Cambridge Tracts in Theoretical Computer Science 31, Cambridge University Press, 1993). The section entitled *Model Checking* contains examples due to John Herbert.

### Contents

| 1 | Har | dware Oriented Programs                            | 1  |

|---|-----|----------------------------------------------------|----|

|   | 1.1 | Hoare logic verification of a multiplier           | 2  |

|   | 1.2 | Words                                              | 8  |

|   | 1.3 | Selecting bits and subwords                        | 8  |

|   | 1.4 | Representing numbers                               | 10 |

|   | 1.5 | Operations on bits and words                       | 11 |

|   | 1.6 | Arithmetic on bits and words                       | 11 |

|   | 1.7 | Verification of a ripple-carry adder               | 12 |

|   | 1.8 | Verification of an add-shift multiplier            | 14 |

|   | 1.9 | From programs to hardware                          | 19 |

| 2 | Des | cribing Hardware Directly in Higher Order Logic    | 23 |

|   | 2.1 | Representing behaviour with predicates             | 23 |

|   |     | 2.1.1 A delayless switch                           | 24 |

|   |     | 2.1.2 An inverter with delay                       | 24 |

|   | 2.2 | Representing circuit structure with predicates     | 25 |

|   | 2.3 | A CMOS inverter                                    | 26 |

|   |     | 2.3.1 Specification of the components              | 26 |

|   |     | 2.3.1.1 Power                                      | 26 |

|   |     | 2.3.1.2 Ground                                     | 27 |

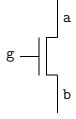

|   |     | 2.3.1.3 $n$ -transistor                            | 27 |

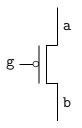

|   |     | 2.3.1.4 $p$ -transistor                            | 27 |

|   |     | 2.3.2 Logic representation of the inverter circuit | 28 |

|   |     | 2.3.3 Verification by proof                        | 28 |

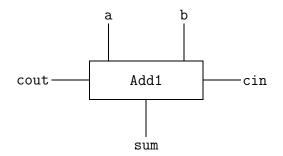

|   | 2.4 | A 1-bit CMOS full adder                            | 30 |

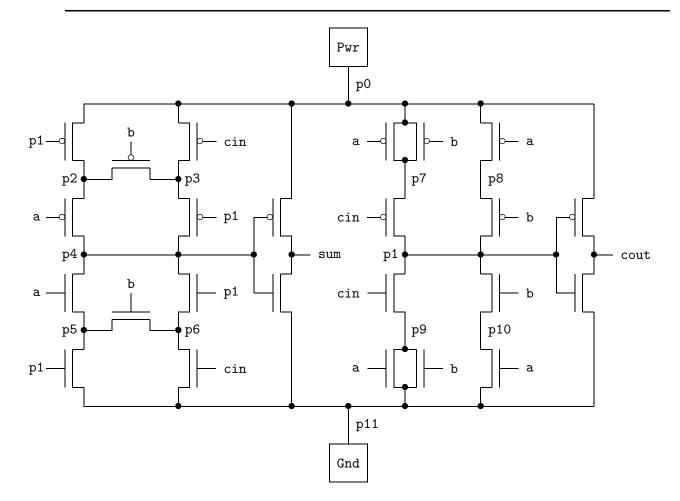

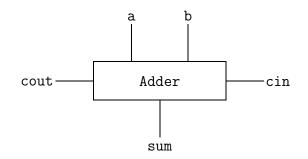

|   |     | 2.4.1 Specification                                | 30 |

|   |     | 2.4.2 Implementation                               | 30 |

|   |     | 2.4.3 Verification                                 | 31 |

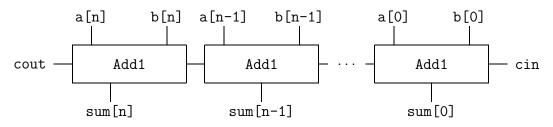

|   | 2.5 | An $n$ -bit adder $\ldots$                         | 32 |

|   |     | 2.5.1 Specification                                | 32 |

|   |     | 2.5.2 Implementation                               | 33 |

|   | 2.6 | Sequential Devices                                 | 34 |

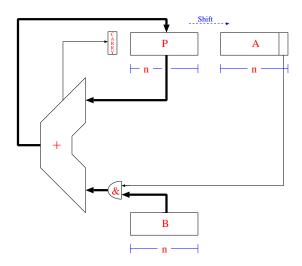

|   | 2.7  | The add-shift multiplier                                                                                                                                              | 5 |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 2.8  | Another multiplier                                                                                                                                                    | 9 |

|   |      | 2.8.1 Some temporal predicates                                                                                                                                        | 1 |

|   |      | 2.8.2 Verification $\ldots \ldots 42$                                                                  | 2 |

|   | 2.9  | An edge-triggered Dtype                                                                                                                                               | 2 |

|   |      | 2.9.1 Specification                                                                                                                                                   | 3 |

|   |      | 2.9.2 Implementation $\ldots \ldots 44$                                                                | 4 |

|   |      | 2.9.3 Verification $\ldots \ldots 44$                                                                  | 5 |

|   | 2.10 | The simple switch model of transistors $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 44$                                                                   | 5 |

|   |      | 2.10.1 Inadequacies of the Simple Switch Model $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 40$                                                                  | 3 |

|   | 2.11 | Fourman's switch model                                                                                                                                                | 3 |

|   | 2.12 | Hoare's switch model                                                                                                                                                  | ) |

|   | 2.13 | Summary                                                                                                                                                               | 1 |

| 3 | Tem  | poral Abstraction 53                                                                                                                                                  | 3 |

|   | 3.1  | Two Problems                                                                                                                                                          | 3 |

|   |      | 3.1.1 Underspecification                                                                                                                                              | 3 |

|   |      | 3.1.2 Inconsistent Models                                                                                                                                             | 7 |

|   | 3.2  | More on Temporal Abstraction                                                                                                                                          | 3 |

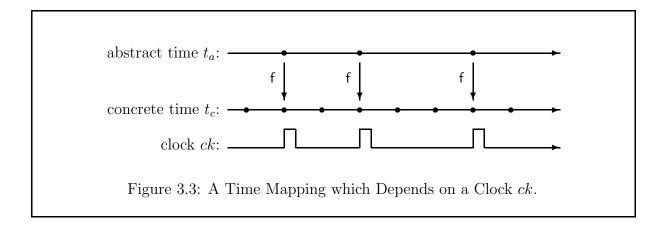

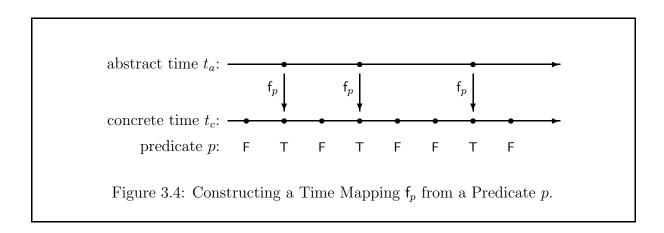

|   |      | 3.2.1 Constructing Mappings between Time Scales                                                                                                                       | ) |

|   |      | 3.2.2 Defining the Function Timeof                                                                                                                                    | 1 |

|   |      | 3.2.2.1 The Relation lstime of $\ldots \ldots \ldots$ | 2 |

|   |      | 3.2.2.2 A Theorem about lstimeof                                                                                                                                      | 2 |

|   |      | $3.2.2.3$ Using lstimeof to Define Timeof $\ldots$                                                                                                                    | 3 |

|   |      | 3.2.3 Using Timeof to Formulate Correctness                                                                                                                           | 1 |

|   | 3.3  | A Simple Example                                                                                                                                                      | 5 |

| 4 | HDI  | Ls Semantics 67                                                                                                                                                       | 7 |

| - | 4.1  | Introduction                                                                                                                                                          |   |

|   | 4.2  | Syntax                                                                                                                                                                |   |

|   | 1.2  | 4.2.1 Expressions                                                                                                                                                     |   |

|   |      | 4.2.2 Event expressions                                                                                                                                               |   |

|   |      | 4.2.3 Statements                                                                                                                                                      |   |

|   |      | 4.2.4 Abbreviations                                                                                                                                                   |   |

|   |      | 4.2.4.1 Case statements                                                                                                                                               |   |

|   |      |                                                                                                                                                                       |   |

|   |                                                      | 4.2.4.2 Continuous assignments                                                                                                                                                                                                                                                                                                                                  |

|---|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.3                                                  | Semantic Pseudo-Code                                                                                                                                                                                                                                                                                                                                            |

|   |                                                      | 4.3.1 Pseudo-code instructions                                                                                                                                                                                                                                                                                                                                  |

|   |                                                      | 4.3.2 The size of a statement $\ldots \ldots \ldots$                                                                                                                                                                                            |

|   |                                                      | 4.3.3 Translation algorithm                                                                                                                                                                                                                                                                                                                                     |

|   |                                                      | 4.3.4 Example translations                                                                                                                                                                                                                                                                                                                                      |

|   | 4.4                                                  | Event Semantics                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                      | 4.4.1 Simulation algorithm $\ldots \ldots .$                                                                                                                                                                                                                                              |

|   | 4.5                                                  | Trace semantics                                                                                                                                                                                                                                                                                                                                                 |

|   |                                                      | 4.5.1 Combinational programs                                                                                                                                                                                                                                                                                                                                    |

|   |                                                      | 4.5.1.1 Transparent latches                                                                                                                                                                                                                                                                                                                                     |

|   |                                                      | $4.5.1.2  \text{Summary}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                                                                                                                                                                                                                      |

|   |                                                      | 4.5.2 Flip-flops                                                                                                                                                                                                                                                                                                                                                |

|   |                                                      | 4.5.3 RTL programs                                                                                                                                                                                                                                                                                                                                              |

|   | 10                                                   |                                                                                                                                                                                                                                                                                                                                                                 |

|   | 4.6                                                  | Cycle semantics                                                                                                                                                                                                                                                                                                                                                 |

| 5 |                                                      | Cycle semantics                                                                                                                                                                                                                                                                                                                                                 |

| 5 |                                                      | lel checking 89                                                                                                                                                                                                                                                                                                                                                 |

| 5 | Mo                                                   | lel checking 89                                                                                                                                                                                                                                                                                                                                                 |

| 5 | <b>Mo</b><br>5.1                                     | lel checking       89         Transition systems       89         Computation Tree Logic (CTL)       90                                                                                                                                                                                                                                                         |

| 5 | <b>Mo</b><br>5.1<br>5.2                              | lel checking       89         Transition systems       89         Computation Tree Logic (CTL)       90                                                                                                                                                                                                                                                         |

| 5 | <b>Mo</b><br>5.1<br>5.2<br>5.3                       | del checking       89         Transition systems       89         Computation Tree Logic (CTL)       90         Using CTL       91                                                                                                                                                                                                                              |

| 5 | Moe<br>5.1<br>5.2<br>5.3<br>5.4                      | del checking       89         Transition systems       89         Computation Tree Logic (CTL)       90         Using CTL       91         Examples of CTL formulae       94                                                                                                                                                                                    |

| 5 | Moe<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5               | del checking       89         Transition systems       89         Computation Tree Logic (CTL)       90         Using CTL       91         Examples of CTL formulae       94         CTL model checking algorithm       99         An example       91                                                                                                          |

| 5 | Moo<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6        | del checking       89         Transition systems       89         Computation Tree Logic (CTL)       90         Using CTL       91         Examples of CTL formulae       94         CTL model checking algorithm       99         An example       97                                                                                                          |

| 5 | Moo<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | del checking       89         Transition systems       89         Computation Tree Logic (CTL)       90         Using CTL       91         Examples of CTL formulae       92         CTL model checking algorithm       93         An example       97         Implementing model checking       99                                                             |

| 5 | Moo<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | del checking       89         Transition systems       90         Computation Tree Logic (CTL)       91         Using CTL       92         Examples of CTL formulae       94         CTL model checking algorithm       99         An example       97         Implementing model checking       99         State transition systems and reachability       100 |

## Hardware Oriented Programs

Floyd-Hoare logic can be used to verify hardware algorithms. This will be illustrated with addition and multiplication. Although natural numbers can be used to represent words, this leads to messy details so a type of words is introduced. Proofs depend on laws relating bit and word operations to arithmetical operations.

Suppose we want to multiply two natural numbers a and b represented as n-bit words in the usual way. Writing ab to abbreviate  $a \times b$ :

$$a = 2^{n-1}a_{n-1} + 2^{n-2}a_{n-2} + \dots + 2^0a_0$$

Here  $a_i$  is the *i*-th bit of the binary representation of a ( $a_0$  being the least significant bit). Then:

$$ab = (2^{n-1}a_{n-1} + 2^{n-2}a_{n-2} + \dots + 2^{0}a_{0})b$$

=  $2^{n-1}a_{n-1}b + 2^{n-2}a_{n-2}b + \dots + 2^{0}a_{0}b$

=  $a_{n-1}2^{n-1}b + a_{n-2}2^{n-2}b + \dots + a_{0}2^{0}b$

Multiplying by 2 corresponds to shifting one place to the left and adding a 0 as the least significant bit. Denote this operation by  $b \mapsto b \sim 0$ , then:

$$2^{0}b = b$$

$$2^{1}b = b \frown 0$$

$$2^{2}b = b \frown 00$$

$$\vdots$$

$$2^{n}b = b \frown \underbrace{0 \cdots 0}_{n \ 0s}$$

Thus the product of a and b is given by the sum:

$$\begin{array}{rcrr}

& a_{0}b \\

+ & a_{1}b \frown 0 \\

+ & a_{2}b \frown 00 \\

+ & a_{3}b \frown 000 \\

& \vdots \\

+ & a_{n-1}b \frown 0 \cdots 0

\end{array}$$

This corresponds to the standard 'high school' algorithm for doing multiplication. In the binary case, the  $i^{\text{th}}$  row is either all zeros (if  $a_i$  is 0) or b shifted i places to the left (if  $a_i$  is 1). If a and b are both n-bit words, then the product needs 2n bits.

### 1.1 Hoare logic verification of a multiplier

Let A[n] denote the *n*-th bit (considered as a number 1 or 0) of the binary representation of A (with A[0] being the least significant bit).

$A[n] = (A \operatorname{div} 2^n) \mod 2$

Define A[m:n] to be the numerical value of the word comprising bits n up to to m of A:

$$\mathbf{A}[m:n] = \begin{cases} 2^{m-n} \mathbf{A}[m] + 2^{m-n-1} \mathbf{A}[m-1] + \cdots + 2^{0} \mathbf{A}[n] & \text{if } m > n \\ \mathbf{A}[n] & \text{if } m = n \\ 0 & \text{if } m < n \end{cases}$$

Below is an annotated specification of the correctness of 'high school' multiplication.

$$\begin{split} \{ \mathbf{A} &= a \ \land \ \mathbf{B} = b \ \land \ a < 2^{\mathbf{N}} \ \land \ b < 2^{\mathbf{N}} \ \land \ \mathbf{N} > 0 \} \\ \mathbf{I} &:= 0; \ \mathsf{PROD} := 0; \\ \{ \mathbf{A} &= a \ \land \ \mathbf{B} = b \ \land \ a < 2^{\mathbf{N}} \ \land \ b < 2^{\mathbf{N}} \ \land \ \mathbf{N} > 0 \ \land \ \mathbf{I} = 0 \ \land \ \mathsf{PROD} = 0 \} \\ \mathsf{WHILE} \ \mathbf{I} < \mathsf{N} \ \mathsf{DO} \ \{ \mathbf{I} \leq \mathsf{N} \ \land \ 2^{\mathbf{I}} \mathbf{A} [\mathsf{N}-1: \mathbf{I}] \, \mathsf{B} + \mathsf{PROD} = ab \} \\ \mathsf{BEGIN} \ \mathsf{PROD} := \mathsf{PROD} \ + \mathbf{A} [\mathbf{I}] \ \times \ (2^{\mathbf{I}} \times \ \mathsf{B}); \\ \mathbf{I} := \mathbf{I} \ + 1; \\ \mathsf{END} \\ \{ \mathsf{PROD} = a \times b \} \end{split}$$

The verification conditions are:

(i)

$$(\mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbb{N}} \land b < 2^{\mathbb{N}} \land \mathbb{N} > 0)$$

$\Rightarrow$

$(\mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbb{N}} \land b < 2^{\mathbb{N}} \land \mathbb{N} > 0 \land 0 = 0 \land 0 = 0)$

The first VC (i) is trivial.

The second VC (ii) is true because if N > 0 and  $A < 2^N$  then A[N-1:0] = A.

For the third VC (iii), consider separately the cases (a) that I+1 = N and (b) that I+1 < N. In case (a) A[N-1:I+1] = 0 and A[N-1:I] = A[I] and the VC follows easily. In case (b) use  $2 \times A[N-1:I+1] + A[I] = A[N-1:I]$ .

The final verification condition (iv) follows because if I = N, then A[N-1:I] = 0.

#### Exercise:

Prove

#### **Exercise:**

Prove

$$\vdash \{ \mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbb{N}} \land b < 2^{\mathbb{N}} \land \mathbb{N} > 0 \}$$

PROD := 0;

FOR I := 0 UNTIL N-1 DO PROD := PROD + A[I] × (2<sup>I</sup>×B)

{PROD = a × b}

#### **Exercise:**

Prove

$$\begin{array}{ll} \vdash \{ \texttt{A} = a & \land \ \texttt{B} = b & \land \ a < 2^{\texttt{N}} & \land \ b < 2^{\texttt{N}} & \land \ \texttt{N} > 0 \} \\ \texttt{PROD} := \texttt{O}; \\ \texttt{FOR I} := \texttt{O} \texttt{ UNTIL N-1 DO BEGIN PROD} := \texttt{PROD} + \texttt{A[I]} \times \texttt{B}; \\ \texttt{B} := 2 \times \texttt{B}; \\ \texttt{END} \\ \{\texttt{PROD} = a \times b \} \end{array}$$

The program in this last exercise corresponds directly to a possible hardware implementation. One has three registers A, B and PROD. Initially PROD is set to 0 and A and B contain the numbers to be multiplied. The I-th step of the multiplication consists in adding  $A[I] \times B$  to PROD and then shifting B one bit to the left (i.e. multiplying it by 2). Register PROD holds the product and so must be 2N-bits wide. However, register B is shifted N times and so it must also be 2N bits wide. This is redundant, because B always just contains the same bits plus some 0s shifted in from the right. An optimisation is to shift PROD to the right instead of shifting B to the left. Then B can be an N-bit register.

The program below exploits this idea.

Note that shifting right corresponds to division by 2.

PROD := 0; FOR I := 0 UNTIL N-1 DO BEGIN PROD := 2<sup>N</sup>A[I]B + PROD; PROD := PROD div 2 END

Consider the case when  $\mathbb{N} = 4$ .

Initially PROD = 0, so PROD div 2 = 0.

The multiplication according to this program proceeds as follows:

$$I = 0$$

, PROD =  $2^4 A[0] B$

PROD =  $2^3 A[0] B$

- $$\begin{split} {\tt I} = 1, \quad {\tt PROD} = 2^4 {\tt A} [1] {\tt B} + 2^3 {\tt A} [0] {\tt B} \\ {\tt PROD} = 2^3 {\tt A} [1] {\tt B} + 2^2 {\tt A} [0] {\tt B} \end{split}$$

- $$\begin{split} \mathbf{I} &= 2, \quad \mathsf{PROD} = 2^4 \mathsf{A} [2] \, \mathsf{B} + 2^3 \mathsf{A} [1] \, \mathsf{B} + 2^2 \mathsf{A} [0] \, \mathsf{B} \\ \quad \mathsf{PROD} &= 2^3 \mathsf{A} [2] \, \mathsf{B} + 2^2 \mathsf{A} [1] \, \mathsf{B} + 2^1 \mathsf{A} [0] \, \mathsf{B} \end{split}$$

- $$\begin{split} \mathbf{I} &= 3, \quad \mathsf{PROD} = 2^4 \mathsf{A} [3] \, \mathsf{B} + 2^3 \mathsf{A} [2] \, \mathsf{B} + 2^2 \mathsf{A} [1] \, \mathsf{B} + 2^1 \mathsf{A} [0] \, \mathsf{B} \\ \quad \mathsf{PROD} &= 2^3 \mathsf{A} [3] \, \mathsf{B} + 2^2 \mathsf{A} [2] \, \mathsf{B} + 2^1 \mathsf{A} [1] \, \mathsf{B} + 2^0 \mathsf{A} [0] \, \mathsf{B} \end{split}$$

Recall the verification conditions for FOR-commands:

#### FOR-commands

The verification conditions generated from

$$\{P\}$$

FOR  $V := E_1$  UNTIL  $E_2$  DO  $\{R\} \subset \{Q\}$

are

- (i)  $P \Rightarrow R[E_1/V]$

- (ii)  $R[E_2+1/V] \Rightarrow Q$

- (iii)  $P \land E_2 < E_1 \Rightarrow Q$

- (iv) the verification conditions generated by

$$\{R \land E_1 \leq V \land V \leq E_2\} C \{R[V+1/V]\}$$

(v) the syntactic condition that neither V, nor any variable occurring in  $E_1$  or  $E_2$ , is assigned to inside C.

The program is easily verified by computing the VCs for:

$$\begin{array}{l} \vdash \left\{ \texttt{A} = a \ \land \ \texttt{B} = b \ \land \ a < 2^{\texttt{N}} \ \land \ b < 2^{\texttt{N}} \ \land \ \texttt{N} > 0 \right\} \\ \texttt{PROD} := \texttt{O}; \ \left\{ \texttt{A} = a \ \land \ \texttt{B} = b \ \land \ a < 2^{\texttt{N}} \ \land \ b < 2^{\texttt{N}} \ \land \ \texttt{N} > 0 \ \land \ \texttt{PROD} = 0 \right\} \\ \texttt{FOR I} := \texttt{O} \ \texttt{UNTIL N-1 DO} \ \left\{ \texttt{PROD} + 2^{\texttt{N}}\texttt{A}[\texttt{N}-1:\texttt{I}]\texttt{B} = 2^{\texttt{N}-\texttt{I}}ab \right\} \\ \texttt{BEGIN} \\ \texttt{PROD} := 2^{\texttt{N}}\texttt{A}[\texttt{I}]\texttt{B} \ + \ \texttt{PROD}; \\ \texttt{PROD} := \texttt{PROD div 2} \\ \texttt{END} \\ \left\{ \texttt{PROD} = ab \right\} \end{array}$$

These are:

(i)

$$(\mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbb{N}} \land b < 2^{\mathbb{N}} \land \mathbb{N} > 0)$$

$\Rightarrow$

$(\mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbb{N}} \land b < 2^{\mathbb{N}} \land \mathbb{N} > 0 \land 0 = 0)$

(ii)

$$(\mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbb{N}} \land b < 2^{\mathbb{N}} \land \mathbb{N} > 0 \land \mathbb{PROD} = 0)$$

$\Rightarrow$

$(\mathbb{PROD} + 2^{\mathbb{N}} \mathbf{A} [\mathbb{N} - 1 : 0] \mathbf{B} = 2^{\mathbb{N} - \mathbb{O}} ab)$

(iii) (PROD +

$$2^{N}A[N-1:N]B = 2^{N-N}ab$$

)

$\Rightarrow$

(PROD =  $ab$ )

(iv)

$$(\mathbf{A} = a \land \mathbf{B} = b \land a < 2^{\mathbb{N}} \land b < 2^{\mathbb{N}} \land \mathbb{N} > 0 \land \mathbb{PROD} = 0) \land \mathbb{N} - 1 < 0$$

$\Rightarrow$

$(\mathbb{PROD} = ab)$

$\begin{array}{ll} (\mathbf{v}) & (\mathtt{PROD} + 2^{\mathtt{N}}\mathtt{A}[\mathtt{N}-1:\mathtt{I}]\mathtt{B} = 2^{\mathtt{N}-\mathtt{I}}ab) & \land & 0 \leq \mathtt{I} & \land & \mathtt{I} \leq \mathtt{N}-\mathtt{1} \\ & \Rightarrow \\ & (((2^{\mathtt{N}}\mathtt{A}[\mathtt{I}]\mathtt{B} + \mathtt{PROD}) \ \mathsf{div} \ 2) + 2^{\mathtt{N}}\mathtt{A}[\mathtt{N}-\mathtt{1}:\mathtt{I}+\mathtt{I}]\mathtt{B} = 2^{\mathtt{N}-(\mathtt{I}+\mathtt{1})}ab) \end{array}$

VCs (i), (ii), (iii) and (iv) are straightforward (note that in the case of (iv) the antecedent N-1 < 0 of the implication is false).

The final VC (v) is also quite easy: assume the antecedent of the implication and then deduce the consequent. Thus assume  $0 \le I \land I \le N-1$  and

$$\mathsf{PROD} + 2^{\mathsf{N}}\mathsf{A}[\mathsf{N}-1:\mathsf{I}]\mathsf{B} = 2^{\mathsf{N}-\mathsf{I}}ab$$

If this equation holds, then as N-I > 0, PROD must be divisible by 2 and hence dividing both sides of the equation by 2:

$$(PROD \text{ div } 2) + 2^{N-1}A[N-1:I]B = 2^{N-(I+1)}ab$$

Now as  $I \leq N-1$  we have:  $A[N-1:I] = 2 \times A[N-1:I+1] + A[I]$  so:

$$(PROD \text{ div } 2) + 2^{N-1}(2 \times A[N-1:I+1] + A[I])B = 2^{N-(I+1)}ab$$

which simplifies to:

$(\texttt{PROD div } 2) + 2^{\texttt{N}}\texttt{A}[\texttt{N}-1:\texttt{I+1}]\texttt{B} + 2^{\texttt{N}-1}\texttt{A}[\texttt{I}]\texttt{B} = 2^{\texttt{N}-(\texttt{I+1})}ab$

which is equivalent to:

$(\texttt{PROD div } 2) + 2^{\texttt{N}}\texttt{A}[\texttt{N}-1:\texttt{I+1}]\texttt{B} + ((2^{\texttt{N}}\texttt{A}[\texttt{I}]\texttt{B}) \texttt{ div } 2) = 2^{\texttt{N}-(\texttt{I+1})}ab$

which can be rearranged to the consequent of the implication of VC (v).

Note that the word representing  $2^{N}A[I]B$  consists of the word representing A[I]B shifted N places to the left. Thus adding  $2^{N}A[I]B$  to an 2N-bit word will not change the N least significant bits, so the addition can be done by adding A[I]B to the N most significant bits and then concatenating the result with the N least significant bits. Thus if  $PROD < 2^{(2N)}$  then:

$$PROD = 2^{N} PROD [2N-1:N] + PROD [N-1:0]$$

hence:

$2^{N}$ A[I]B + PROD =  $2^{N}$ (A[I]B + PROD[2N-1:N]) + PROD[N-1:0]

and the first sum on the right hand side of this equation (the one in the brackets) is the addition to two N-bit numbers, which might require N+1 bits.

Let us split PROD into two N-bit variables PROD1 and PROD2 holding PROD[N-1:0] and PROD[2N-1:N], respectively. Thus:

$PROD = 2^{N}PROD2 + PROD1$

Let SUM be an N+1 bit variable for holding the result of A[I]B + PROD2.

Then the program above can then be reformulated as:

**Exercise:** Write an annotated partial correctness specification of this program that says that it does multiplication, generate the verification conditions and outline why they are true. [Warning: I have not formally verified this program – it might have bugs!]

As a final optimisation, the initially unused space in PROD1 can be used to store A. After each right shift (div 2) a bit of A is lost, but we can cunningly arrange that the I-th bit of A is the 0-th bit of PROD1 on iteration I so bits of A are only lost after they have been 'used'.

**Exercise:** Write an annotated partial correctness specification of this program that says that it does multiplication, generate the verification conditions and outline why they are true. [Warning: I have not formally verified this program – it might have bugs!]

The multiplier discussed above modelled *n*-bit words as a natural numbers less than  $2^n$ . Hardware operations are usually specified in terms of bit manipulations like shifts, word concatenations, subword extractions etc. Although these operations can be represented arithmetically (left-shift is multiplication by 2, right-shift if division by 2 etc.) it turns out to be convenient to work with a separate type of words. An important advantage of this is that words can carry their size and so the concatenation of an *m*-bit word  $w_1$  with an *n*-bit word  $w_2$  can be unambiguously written as  $w_1 \neg w_2$ . The arithmetical counterpart to concatenation needs to be parameterised on *n*. Thus, if  $w_1$  denotes number *a* and  $w_2$  denotes b then  $w_1 \frown w_2$  denotes  $2^n a + b$  – an expression depending on n. Thus  $a \frown b$  doesn't make sense and one would need to write something like  $a \frown_n b$ , – i.e. have a family of operators  $\frown_n$  instead of a single  $\frown$ .

For such reasons, a type of words is useful.

### 1.2 Words

A word is a fixed-size array of bits. Bits are represented by the truth values T and F of type *bool*. Following standard practice, the two numerals 1 and 0 will sometimes be used to denote the bits T and F, respectively.

The 'empty word' has zero length and all other words have length greater than zero. The length of a word is denoted by |w|.

Two words are equal if they have both the same length and the same bits:

$$(w_1 = w_2) \equiv (|w_1| = |w_2|) \land \forall i. \ i < |w_1| \Rightarrow w_1[i] = w_2[i]$$

Individual words will be written in the stardard way with the least significant bit at the right. For example, here is an 8-bit word: 00011011:

$$|00011011| = 8$$

If b is a bit and n > 0 then  $b^n$  is the concatenation of n bs, e.g.  $0^3 = 000$ . Clearly  $|b^n| = n$ .

### **1.3** Selecting bits and subwords

The  $n^{\text{th}}$  bit of a word w will be denoted by w[n], where the least significant bit is considered to be the  $0^{\text{th}}$  bit. Thus:

$$b_{n-1}\cdots b_0[i] = b_i$$

When  $n \ge |w|$  the convention adopted is that w[n] = 0. Thus in general:

$$b_{n-1} \cdots b_0 [i] = (i < n \rightarrow b_i \mid 0)$$

For  $m \ge n$  the notation w[m:n] denotes the word consisting of bits m to n of w.

$$b_{n-1}\cdots b_i\cdots b_j\cdots b_0[i:j] = b_i\cdots b_j$$

The convention is adopted that if m < n then w[m:n] denotes the empty word, and if either m > |w| or n > |w|, then w is padded (at its left) with 0s. Thus if  $m \ge n$ , then:

$$|w[m:n]| = m-n+1$$

For example:

$$100101[4:1] = 0010$$

$$100101[7:1] = 0010010$$

$$100101[8:6] = 000$$

$$100101[1:2] = \text{the empty word}$$

w[n:n] denotes the 1-bit word consisting of w[n]. The type of all words is word, thus w[n]: bool but w[n:n]: word. Thus for  $m \ge n$ , the subword selection w[m:n] is defined by:

$$(w[m:n])[i] = (i+n \le m \to w[i+n] \mid 0)$$

Obvious facts can be derived from this definition, for example:

$$\begin{split} |w| > 0 & \Rightarrow w[|w|-1:0] = w \\ p+n \le m & \Rightarrow w[m:n][p:q] = w[p+n:q+n] \end{split}$$

Each of these conditional equations are verified by first checking the equated words have the same length (obvious) and then checking that corresponding bits are equal. In the first example:

$$\begin{array}{rcl} w\,[|w|-1:0]\,[i] &=& (i\!+\!0 \leq |w|\!-\!1 \to w\,[i\!+\!0] \mid 0) \\ &=& (i < |w| \to w\,[i] \mid 0) \\ &=& w\,[i] \end{array}$$

For the second example:

$$\begin{array}{ll} (w\,[m:n]\,[p:q]\,)\,[i] &=& (i+q \leq p \to w\,[m:n]\,[i+q] \mid 0) \\ &=& (i+q \leq p \to ((i+q)+n \leq m \to w\,[(i+q)+n] \mid 0) \mid 0) \\ &=& ((i+q \leq p) \land ((i+q)+n \leq m) \to w\,[(i+q)+n] \mid 0) \end{array}$$

and

$$w[p+n:q+n][i] = (i+(q+n) \le p+n \to w[i+(q+n)] \mid 0) = (i+q \le p \to w[i+(q+n)] \mid 0)$$

Now, if  $p + n \le m$  then clearly:

$$(i+q \le p) \implies ((i+q)+n \le m)$$

hence (as  $A \Rightarrow B \equiv A \land B = A$ ):

$$(i+q \le p) \land ((i+q)+n \le m) \equiv (i+q \le p)$$

and so (w[m:n][p:q])[i] = w[p+n:q+n][i].

Bits and 1-bit words are different types. The word corresponding to a bit b is Bw(b). Thus: Bw(b)[0] = b.

### 1.4 Representing numbers

Words represent natural numbers and integers in a standard way:

- Natural number:  $b_{n-1} \cdots b_0$  represents  $2^{n-1} \times b_{n-1} + 2^{n-2} \times b_{n-2} + \cdots + 2^0 \times b_0$

- Integer<sup>1</sup>:  $b_{n-1} \cdots b_0$  represents  $-2^{n-1} \times b_{n-1} + 2^{n-2} \times b_{n-2} + \cdots + 2^0 \times b_0$

The notation V(w) will be used to denote the natural number represented by a word, i.e.:

$$\mathsf{V}(b_{n-1}\cdots b_0) = 2^{n-1} \times b_{n-1} + 2^{n-2} \times b_{n-2} + \cdots + 2^0 \times b_0$$

Words can, of course, also represent other numeric or non-numeric values (e.g. floating point numbers or opcodes).

The number represented by a bit b will be denoted by Bv(b), thus:

$$Bv(T) = 1$$

and  $Bv(F) = 0$

Word operations are related to arithmetical operations via div and mod, where

$m \operatorname{div} n = \operatorname{integer} part of \operatorname{dividing} m \operatorname{by} n$

$m \mod n$  = remainder after dividing m by n

The fundamental properties relating div and mod are:

$$n \times (m \text{ div } n) + m \mod n = m$$

$(m \mod n) < n$

Note the following:

$$Bv(w[n]) = (V(w) \text{ div } 2^n) \mod 2$$

$$V(w[m:n]) = (V(w) \text{ div } 2^n) \mod 2^{m-n+1}$$

$$V(w[n:0]) = 2^n \times Bv(w[n]) + V(w[n-1:0])$$

Whilst there is a canonical natural number V(w) associated with a word w, there is no canonical inverse function, since e.g.:

$$\begin{array}{rcl} \mathsf{V}(101) &=& 5\\ \mathsf{V}(0101) &=& 5\\ \mathsf{V}(00101) &=& 5\\ &\vdots \end{array}$$

For any size n, the function W n maps a number m to the unique n-bit word w such that  $V(w) = m \mod 2^n$ , i.e.:

$$V(W \ n \ m) = m \mod 2^n$$

$$W \ |w| \ (V(w)) = w$$

For example, W 5 143 = 01111.

$<sup>^1\</sup>mathrm{Two's}$  complement representation.

### 1.5 Operations on bits and words

The standard infixed binary operators of Boolean algebra are  $\land$  ('and'),  $\lor$  ('or'),  $\oplus$  ('exclusive or' or 'unequal') and = ('if and only if' or 'equals'). Note that these are all commutative and associative. Negation,  $\neg$ , is a prefixed unary operator. These operators will be extended (overloaded) to operate bitwise on words.

The concatenation of an *m*-bit word  $w_1$  with an *n*-bit word  $w_2$  is denoted by  $w_1 \neg w_2$ . This is an *m*+*n*-bit word. Note the following properties:

$$\begin{array}{rcl} 0 < |w_2| & \Rightarrow & (w_1 \neg w_2) \left[ |w_2| - 1 : 0 \right] & = & w_2 \\ 0 < |w_1| & \Rightarrow & (w_1 \neg w_2) \left[ |w_1| + |w_2| - 1 : |w_2| \right] & = & w_1 \\ & & V(w_1 \neg w_2) & = & 2^{|w_2|} V(w_1) + V(w_2) \\ p < |w_2| & \Rightarrow & (w_1 \neg w_2) \left[ p : q \right] & = & w_2 \left[ p : q \right] \\ p \ge q \land q \ge |w_2| & \Rightarrow & (w_1 \neg w_2) \left[ p : q \right] & = & w_1 \left[ p - |w_2| : q - |w_2| \right] \\ p \ge |w_2| \land q < |w_2| & \Rightarrow & (w_1 \neg w_2) \left[ p : q \right] & = & w_1 \left[ p - |w_2| : 0 \right] \neg w_2 \left[ |w_2| - 1 : q \right] \end{array}$$

The 'array update' notation  $w\{n \leftarrow b\}$  denotes a word identical to w, except that w[n] = b. Note that:

$$V(w\{n \leftarrow b\}[n:0]) = 2^n \times Bv(b) + V(w[n-1:0])$$

### 1.6 Arithmetic on bits and words

The sum of two bits a and b and a carry-in bit c is computed by  $a \oplus b \oplus c$  and the carry-out by  $(a \wedge b) \lor (c \land (a \oplus b))$ . This is verified by the equations:

$$Bv(a \oplus b \oplus c) = (Bv(a) + Bv(b) + Bv(c)) \mod 2$$

$$Bv((a \wedge b) \lor (c \land (a \oplus b))) = (Bv(a) + Bv(b) + Bv(c)) \operatorname{div} 2$$

These are most simply verified by exhaustive enumeration. The equation for the sum is verified by:

| a | b | С | $Bv(a \oplus b \oplus c)$ | $(Bv(a) + Bv(b) + Bv(c)) \bmod 2$ |

|---|---|---|---------------------------|-----------------------------------|

| 1 | 1 | 1 | 1                         | 1                                 |

| 1 | 1 | 0 | 0                         | 0                                 |

| 1 | 0 | 1 | 0                         | 0                                 |

| 1 | 0 | 0 | 1                         | 1                                 |

| 0 | 1 | 1 | 0                         | 0                                 |

| 0 | 1 | 0 | 1                         | 1                                 |

| 0 | 0 | 1 | 1                         | 1                                 |

| 0 | 0 | 0 | 0                         | 0                                 |

| a | b | С | $Bv((a \land b) \lor (c \land (a \oplus b)))$ | $(Bv(a) + Bv(b) + Bv(c)) \operatorname{div} 2$ |

|---|---|---|-----------------------------------------------|------------------------------------------------|

| 1 | 1 | 1 | 1                                             | 1                                              |

| 1 | 1 | 0 | 1                                             | 1                                              |

| 1 | 0 | 1 | 1                                             | 1                                              |

| 1 | 0 | 0 | 0                                             | 0                                              |

| 0 | 1 | 1 | 1                                             | 1                                              |

| 0 | 1 | 0 | 0                                             | 0                                              |

| 0 | 0 | 1 | 0                                             | 0                                              |

| 0 | 0 | 0 | 0                                             | 0                                              |

The equation for the carry is verified by:

The addition of two non-empty words  $w_1$  and  $w_2$  is denoted by  $w_1 \uplus w_2$  and defined by:

$$w_1 \uplus w_2 = \mathsf{W} (\max(|w_1|, |w_2|) + 1) (\mathsf{V}(w_1) + \mathsf{V}(w_2))$$

$w_1 \uplus w_2$  satisfies:

$$|w_1 \uplus w_2| = \max(|w_1|, |w_2|) + 1$$

$$\mathsf{V}(w_1 \uplus w_2) = \mathsf{V}(w_1) + \mathsf{V}(w_2)$$

$$w \uplus (\mathsf{W} |w| 0) = 0 \neg w$$

### 1.7 Verification of a ripple-carry adder

Let R be:

$2^{I}\mathsf{Bv}(\mathsf{CARRY}) + \mathsf{V}(\mathsf{SUM}[\mathsf{I}-\mathsf{1}:\mathsf{0}]) = \mathsf{V}(\mathsf{A}[\mathsf{I}-\mathsf{1}:\mathsf{0}]) + \mathsf{V}(\mathsf{B}[\mathsf{I}-\mathsf{1}:\mathsf{0}])$  $\land \mathsf{A} = w_1 \land \mathsf{B} = w_2$

Consider the following annotated specification:

$$\begin{split} & \{ \mathbf{A} = w_1 \ \land \ \mathbf{B} = w_2 \ \land \ \mathsf{SUM} = \mathsf{W} \ \mathsf{N} \ \mathbf{0} \ \land \ \mathsf{CARRY} = \mathsf{F} \\ & \land \ |w_1| \leq \mathsf{N} \ \land \ |w_2| \leq \mathsf{N} \ \land \ \mathsf{N} > \mathbf{0} \} \\ & \mathsf{FOR} \ \mathsf{I} \ := \ \mathsf{0} \ \mathsf{UNTIL} \ \mathsf{N} - \mathsf{1} \ \mathsf{DO} \ \{ R \} \\ & \mathsf{BEGIN} \\ & \mathsf{SUM}[\mathsf{I}] := \mathsf{A}[\mathsf{I}] \oplus \mathsf{B}[\mathsf{I}] \oplus \mathsf{CARRY}; \\ & \mathsf{CARRY} := (\mathsf{A}[\mathsf{I}] \land \mathsf{B}[\mathsf{I}]) \lor (\mathsf{CARRY} \land (\mathsf{A}[\mathsf{I}] \oplus \mathsf{B}[\mathsf{I}])); \\ & \mathsf{END} \\ & \{ \mathsf{A} = w_1 \ \land \ \mathsf{B} = w_2 \\ & \land \ 2^{\mathsf{N}} \mathsf{Bv}(\mathsf{CARRY}) + \mathsf{V}(\mathsf{SUM}[\mathsf{N} - \mathsf{1} : \mathsf{0}]) = \mathsf{V}(\mathsf{A}[\mathsf{N} - \mathsf{1} : \mathsf{0}]) + \mathsf{V}(\mathsf{B}[\mathsf{N} - \mathsf{1} : \mathsf{0}]) \} \end{split}$$

Here, A and B are N-bit words, SUM and CARRY are bits (truthvalues) and I is an integer. The verification conditions (VCs) are:

(i)

$$(\mathbf{A} = w_1 \land \mathbf{B} = w_2 \land \text{SUM} = \mathbf{W} \land \mathbf{N} \circ \mathbf{A} \text{ CARRY} = \mathbf{F}$$

$\land |w_1| \leq \aleph \land |w_2| \leq \aleph \land \aleph > 0)$

$\Rightarrow$

$(2^0 \mathsf{Bv}(\mathsf{CARRY}) + \mathsf{V}(\mathsf{SUM}[\mathsf{O}-1:\mathsf{O}]) = \mathsf{V}(\mathsf{A}[\mathsf{O}-1:\mathsf{O}]) + \mathsf{V}(\mathsf{B}[\mathsf{O}-1:\mathsf{O}]))$

$\land \mathsf{A} = w_1 \land \mathsf{B} = w_2)$

(ii)  $(2^N \mathsf{Bv}(\mathsf{CARRY}) + \mathsf{V}(\mathsf{SUM}[\mathsf{N}-1:\mathsf{O}]) = \mathsf{V}(\mathsf{A}[\mathsf{N}-1:\mathsf{O}]) + \mathsf{V}(\mathsf{B}[\mathsf{N}-1:\mathsf{O}]))$

$\land \mathsf{A} = w_1 \land \mathsf{B} = w_2)$

$\Rightarrow$

$(\mathsf{A} = w_1 \land \mathsf{B} = w_2)$

$\Rightarrow$

$(\mathsf{A} = w_1 \land \mathsf{B} = w_2)$

$\Rightarrow$

$(\mathsf{A} = w_1 \land \mathsf{B} = w_2)$

$(\mathsf{III}) (\mathsf{A} = w_1 \land \mathsf{B} = w_2 \land \mathsf{SUM} = \mathsf{W} \land \mathsf{O} \land \mathsf{CARRY} = \mathsf{F})$

$(\mathsf{IIII}) (\mathsf{A} = w_1 \land \mathsf{B} = w_2 \land \mathsf{SUM} = \mathsf{W} \land \mathsf{O} \land \mathsf{CARRY} = \mathsf{F})$

(iii)

$$(\mathbf{A} = w_1 \land \mathbf{B} = w_2 \land \mathbf{SOM} = \mathbf{V} \lor \mathbf{N} \lor \mathbf{O} \land \mathbf{CARRI} =$$

$\land |w_1| \le \mathbf{N} \land |w_2| \le \mathbf{N} \land \mathbf{N} > \mathbf{O})$

$\land (\mathbf{N} - \mathbf{1} < \mathbf{O}) \Rightarrow (\cdots)$

(iv) VCs from

$$\{ R \land 0 \leq I \land I \leq N-1 \}$$

SUM[I]:=A[I]  $\oplus$  B[I]  $\oplus$  CARRY;

CARRY:=(A[I] \land B[I])  $\lor$  (CARRY  $\land$  (A[I]  $\oplus$  B[I]));

$\{ R[I+1/I] \}$

The VCs (i), (ii) and (iii) are obviously true.

There is one VC from (iv):

$$\begin{array}{l} \left(2^{\mathbf{I}} \times \mathsf{Bv}(\mathsf{CARRY}) + \mathsf{V}(\mathsf{SUM}[\mathsf{I}-1:0]) = \mathsf{V}(\mathsf{A}[\mathsf{I}-1:0]) + \mathsf{V}(\mathsf{B}[\mathsf{I}-1:0]) \\ \wedge \ \mathsf{A} = w_1 \ \wedge \ \mathsf{B} = w_2\right) \ \wedge \ 0 \leq \mathsf{I} \ \wedge \ \mathsf{I} \leq \mathsf{N}-\mathsf{I} \\ \Rightarrow \\ \left(\left(2^{\mathbf{I}+1} \times \mathsf{Bv}((\mathsf{A}[\mathsf{I}] \land \mathsf{B}[\mathsf{I}]) \lor (\mathsf{CARRY} \land (\mathsf{A}[\mathsf{I}] \oplus \mathsf{B}[\mathsf{I}]))) \\ + \ \mathsf{V}(\mathsf{SUM}\{\mathsf{I} \leftarrow \mathsf{A}[\mathsf{I}] \oplus \mathsf{B}[\mathsf{I}] \oplus \mathsf{CARRY}\}[\mathsf{I}:0]) \\ = \ \mathsf{V}(\mathsf{A}[\mathsf{I}:0]) + \mathsf{V}(\mathsf{B}[\mathsf{I}:0])) \\ \wedge \ \mathsf{A} = w_1 \ \wedge \ \mathsf{B} = w_2 \right) \end{array}$$

It was previously established by exhaustive enumeration that:

$$\begin{aligned} & \mathsf{Bv}(a \oplus b \oplus c) = (\mathsf{Bv}(a) + \mathsf{Bv}(b) + \mathsf{Bv}(c)) \bmod 2 \\ & \mathsf{Bv}((a \wedge b) \lor (c \land (a \oplus b))) = (\mathsf{Bv}(a) + \mathsf{Bv}(b) + \mathsf{Bv}(c)) \operatorname{div} 2 \end{aligned}$$

Recall also that:

$$V(w\{n \leftarrow b\}[n:0]) = 2^n \times Bv(b) + V(w[n-1:0])$$

Thus:

$$\begin{array}{l} 2^{\texttt{I+1}} \times \mathsf{Bv}((\texttt{A}[\texttt{I}] \land \texttt{B}[\texttt{I}]) \lor (\texttt{CARRY} \land (\texttt{A}[\texttt{I}] \oplus \texttt{B}[\texttt{I}]))) \\ + \mathsf{V}(\texttt{SUM}\{\texttt{I} \leftarrow \texttt{A}[\texttt{I}] \oplus \texttt{B}[\texttt{I}] \oplus \texttt{CARRY}\}\texttt{[I:0]}) \\ = \mathsf{V}(\texttt{A}\texttt{[I:0]}) + \mathsf{V}(\texttt{B}\texttt{[I:0]}) \end{array}$$

is equivalent to

$$\begin{array}{l} 2^{\texttt{I+1}} \times \big( (\texttt{Bv}(\texttt{A[I]}) + \texttt{Bv}(\texttt{B[I]}) + \texttt{Bv}(\texttt{CARRY})) \ \texttt{div} \ 2 \big) \\ + \ 2^{\texttt{I}} \times \big( (\texttt{Bv}(\texttt{A[I]}) + \texttt{Bv}(\texttt{B[I]}) + \texttt{Bv}(\texttt{CARRY})) \ \texttt{mod} \ 2 \big) + \mathsf{V}(\texttt{SUM}[\texttt{I-1}:\texttt{0}]) \\ = \ \mathsf{V}(\texttt{A}[\texttt{I}:\texttt{0}]) + \mathsf{V}(\texttt{B}[\texttt{I}:\texttt{0}]) \end{array}$$

Using  $V(w[n:0]) = 2^n \times Bv(w[n]) + V(w[n-1:0])$  yields:

$$\begin{array}{l} 2^{\texttt{I+1}} \times \big((\texttt{Bv}(\texttt{A[I]}) + \texttt{Bv}(\texttt{B[I]}) + \texttt{Bv}(\texttt{CARRY})) \ \texttt{div} \ 2\big) \\ + \ 2^{\texttt{I}} \times \big((\texttt{Bv}(\texttt{A[I]}) + \texttt{Bv}(\texttt{B[I]}) + \texttt{Bv}(\texttt{CARRY})) \ \texttt{mod} \ 2\big) + \texttt{V}(\texttt{SUM}[\texttt{I-1}:\texttt{0}]) \\ = \ 2^{\texttt{I}} \times \texttt{Bv}(\texttt{A[I]}) + \texttt{V}(\texttt{A}[\texttt{I-1}:\texttt{0}]) + 2^{\texttt{I}} \times \texttt{Bv}(\texttt{B[I]}) + \texttt{V}(\texttt{B}[\texttt{I-1}:\texttt{0}]) \end{array}$$

Now, the antecendent of VC (iv) contains:

$$2^{I} \times Bv(CARRY) + V(SUM[I-1:0]) = V(A[I-1:0]) + V(B[I-1:0])$$

hence the first conjunct of the consequent can be simplified to:

$$\begin{array}{l} 2^{\texttt{I}+1} \times \left( (\texttt{Bv}(\texttt{A[I]}) + \texttt{Bv}(\texttt{B[I]}) + \texttt{Bv}(\texttt{CARRY})) \ \texttt{div} \ 2 \right) \\ + \ 2^{\texttt{I}} \times \left( (\texttt{Bv}(\texttt{A[I]}) + \texttt{Bv}(\texttt{B[I]}) + \texttt{Bv}(\texttt{CARRY})) \ \texttt{mod} \ 2 \right) + \texttt{V}(\texttt{SUM}[\texttt{I}-\texttt{1}:\texttt{0}]) \\ = \ 2^{\texttt{I}} \times \texttt{Bv}(\texttt{CARRY}) + \texttt{V}(\texttt{SUM}[\texttt{I}-\texttt{1}:\texttt{0}]) + 2^{\texttt{I}} \times \texttt{Bv}(\texttt{A[I]}) + 2^{\texttt{I}} \times \texttt{Bv}(\texttt{B[I]}) \end{array}$$

Cancelling V(SUM[I-1:0]) and then dividing by  $2^{I}$  yields:

$$2 \times ((Bv(A[I]) + Bv(B[I]) + Bv(CARRY)) \text{ div } 2) \\ + ((Bv(A[I]) + Bv(B[I]) + Bv(CARRY)) \text{ mod } 2) \\ = Bv(CARRY) + Bv(A[I]) + Bv(B[I])$$

This is just an instance of  $n \times (m \operatorname{div} n) + m \mod n = m$ . Thus VC (iv) is established.

### 1.8 Verification of an add-shift multiplier

The notation  $b \cdot w$ , where b is a bit (truth value) and w a word, denotes w if  $b = \mathsf{T}$  and  $\mathsf{W} | w | 0$  if  $b = \mathsf{F}$ , i.e.  $b \cdot w = (b \to w | \mathsf{W} | w | 0)$ . Note that:

$$\mathsf{V}(b \cdot w) = \mathsf{Bv}(b) \times \mathsf{V}(w)$$

The product of two natural numbers represented as *n*-bit words  $w_1$  and  $w_2$  is a word w such that (writing  $m \times n$  as mn):

$$V(w) = V(w_1)V(w_2)$$

=  $(2^{n-1}Bv(w_1[n-1]) + 2^{n-2}Bv(w_1[n-2]) + \dots + 2^0Bv(w_1[0]))V(w_2)$

=  $2^{n-1}Bv(w_1[n-1])V(w_2) + 2^{n-2}Bv(w_1[n-2])V(w_2) + \dots + 2^0Bv(w_1[0])V(w_2)$

=  $2^{n-1}V(w_1[n-1] \cdot w_2) + 2^{n-2}V(w_1[n-2] \cdot w_2) + \dots + 2^0V(w_1[0] \cdot w_2)$

Multiplying by 2 corresponds to shifting one place to the left:

$$2^{0}\mathsf{V}(w) = \mathsf{V}(w)$$

$$2^{1}\mathsf{V}(w) = \mathsf{V}(w \frown 0)$$

$$2^{2}\mathsf{V}(w) = \mathsf{V}(w \frown 00)$$

$$\vdots$$

$$2^{n}\mathsf{V}(w) = \mathsf{V}(w \frown \underbrace{0 \cdots 0}_{n \ 0s})$$

Thus the product of  $w_1$  and  $w_2$  is given by adding:

$$w_{1}[0] \cdot w_{2}$$

$$w_{1}[1] \cdot w_{2} \sim 0$$

$$w_{1}[2] \cdot w_{2} \sim 00$$

$$w_{1}[3] \cdot w_{2} \sim 000$$

$$\vdots$$

$$w_{1}[n-1] \cdot w_{2} \sim 0 \cdots 0$$

This is the 'high school' algorithm for doing multiplication described earlier.

The following annotated specification expresses the correctness of this algorithm:

$$\{ \mathsf{V}(\mathsf{A}) = a \land \mathsf{V}(\mathsf{B}) = b \land \mathsf{PROD} = \mathsf{W}(2\mathsf{N})0 \land |\mathsf{A}| \leq \mathsf{N} \land |\mathsf{B}| \leq \mathsf{N} \land \mathsf{N} > 0 \}$$

$$\mathsf{FOR I} := \mathsf{O} \text{ UNTIL N-1 DO } \{ 2^{\mathsf{I}} \mathsf{V}(\mathsf{A}[\mathsf{N-1}:\mathsf{I}])b + \mathsf{V}(\mathsf{PROD}) = ab \land \mathsf{V}(\mathsf{B}) = 2^{\mathsf{I}}b \}$$

$$\mathsf{BEGIN}$$

$$\mathsf{PROD} := \mathsf{PROD} \ \uplus \mathsf{A}[\mathsf{I}] \cdot \mathsf{B};$$

$$\mathsf{B} := \mathsf{B} \neg \mathsf{O}$$

$$\mathsf{END}$$

$$\{ \mathsf{V}(\mathsf{PROD}) = ab \}$$

The VCs for the correctness of the 'high school' multiplication algorithm are:

(i)  $(V(A) = a \land V(B) = b \land PROD = W(2N)0 \land |A| \le N \land |B| \le N \land N > 0)$   $\Rightarrow$  $(2^{0}V(A[N-1:0])b + V(PROD) = ab \land V(B) = 2^{0}b)$

(ii)

$$(2^{\mathbb{N}} \mathsf{V}(\mathsf{A}[\mathbb{N}-1:\mathbb{N}])b + \mathsf{V}(\mathsf{PROD}) = ab \land \mathsf{V}(\mathsf{B}) = 2^{\mathbb{N}}b) \Rightarrow (\mathsf{PROD} = ab)$$

- (iii)  $(V(A) = a \land V(B) = b \land PROD = W(2N)0 \land |A| \le N \land |B| \le N \land N > 0) \land N-1 < 0$   $\Rightarrow$ (PROD = ab)

- (iv)  $(2^{\mathbb{I}} \mathsf{V}(\mathsf{A}[\mathsf{N-1}:\mathbb{I}])b + \mathsf{V}(\mathsf{PROD}) = ab \land \mathsf{V}(\mathsf{B}) = 2^{\mathbb{I}}b) \land 0 \leq \mathbb{I} \land \mathbb{I} \leq \mathsf{N-1}$   $\Rightarrow$  $2^{\mathbb{I}+1} \mathsf{V}(\mathsf{A}[\mathsf{N-1}:\mathbb{I}+1])b + \mathsf{V}(\mathsf{PROD} \uplus \mathsf{A}[\mathbb{I}] \cdot \mathsf{B}) = ab \land \mathsf{V}(\mathsf{B} \cap 0) = 2^{\mathbb{I}+1}b$

# **Exercise:** Check whether these verification conditions are true. (Warning: quite likely to be wrong!)

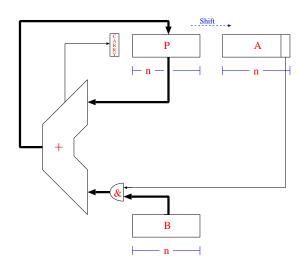

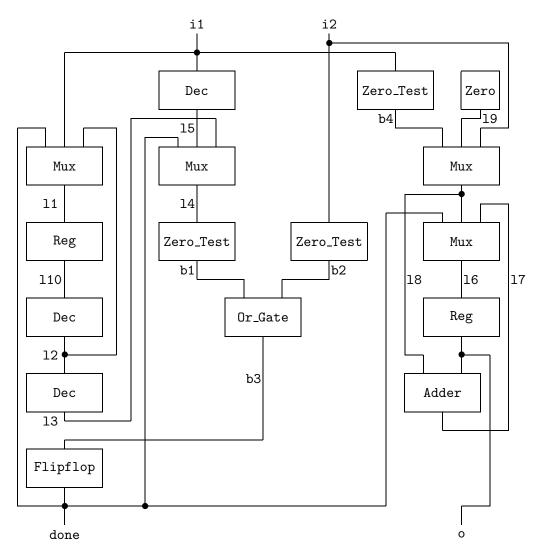

Here is a standard textbook multiplier: <sup>2</sup>

In the program below, the product is computed in a single 2N-bit variable R. The N high order bits of R correspond the register P (after CARRY has been right-shifted into P); the N low-order bits of R correspond to register A.

At the  $I^{\text{th}}$  iteration R[2N-1:N-I] holds the result of adding the first I rows of the sum:

$$w_{1}[0] \cdot w_{2}$$

$$w_{1}[1] \cdot w_{2} \sim 0$$

$$w_{1}[2] \cdot w_{2} \sim 00$$

$$w_{1}[3] \cdot w_{2} \sim 000$$

$$\vdots$$

$$w_{1}[n-1] \cdot w_{2} \sim 0 \cdots 0$$

and  $\mathbb{R}[\mathbb{N}-\mathbb{I}-\mathbb{I}:0]$  holds  $w_1[\mathbb{N}-\mathbb{I}:\mathbb{I}]$ . Initially  $w_1$  is loaded into the bottom half of  $\mathbb{R}$ , but during the computation this is gradually overwritten by the low-order bits of the product. The variable  $\mathbb{B}$  holds  $w_2$ .

Let

$$\begin{split} \mathcal{I}_1 &\equiv w_1 [\mathtt{N} - \mathtt{1} : \mathtt{I}] = \mathtt{R} [\mathtt{N} - \mathtt{1} - \mathtt{I} : \mathtt{O}] \\ \mathcal{I}_2 &\equiv \mathsf{V} (\mathtt{R} [\mathtt{2} \mathtt{N} - \mathtt{1} : \mathtt{N} - \mathtt{I}]) = \mathsf{V} (w_1 [\mathtt{I} - \mathtt{1} : \mathtt{O}]) \times \mathsf{V} (\mathtt{B}) \end{split}$$

Consider:

<sup>&</sup>lt;sup>2</sup>Computer Architecture: A Quantitative Approach by Hennessy and Patterson (ISDBN 1-55860-069-8).

$$\{ \mathbf{R} = (\mathbf{W} \ \mathbf{N} \ \mathbf{0}) \frown w_1 \land \mathbf{B} = w_2 \land |w_1| \le \mathbf{N} \land |w_2| \le \mathbf{N} \land \mathbf{N} > \mathbf{0} \}$$

FOR I := 0 UNTIL N-1 DO  $\{ \mathcal{I}_1 \land \mathcal{I}_2 \land \mathbf{B} = w_2 \}$

R := (R[0] • B  $\uplus$  R[2N-1:N])  $\frown$  R[N-1:1]

$\{ \mathbf{V}(\mathbf{R}[2\mathbf{N}-1:\mathbf{0}]) = \mathbf{V}(\mathbf{w}_1) \times \mathbf{V}(\mathbf{w}_2) \land \mathbf{B} = \mathbf{w}_2 \}$

The verification conditions are:

(i)

$$(\mathbf{R} = (\mathbf{W} \ \mathbf{N} \ \mathbf{0}) \frown w_1 \land \mathbf{B} = w_2 \land |w_1| \le \mathbf{N} \land |w_2| \le \mathbf{N} \land \mathbf{N} >$$

$\Rightarrow$

$(\mathcal{I}_1 \land \mathcal{I}_2 \land \mathbf{B} = w_2)[\mathbf{0}/\mathbf{I}]$

(ii)  $(\mathcal{I}_1 \land \mathcal{I}_2 \land \mathbf{B} = w_2)[\mathbf{N}/\mathbf{I}]$

$\Rightarrow$

$(\mathbf{V}(\mathbf{R}[2\mathbf{N}-\mathbf{1}:\mathbf{0}]) = \mathbf{V}(\mathbf{w}_1) \times \mathbf{V}(\mathbf{w}_2) \land \mathbf{B} = \mathbf{w}_2)$

(iii)

$$(\dots \land \mathbb{N} > 0) \land (\mathbb{N} - 1 < 0) \Rightarrow (\dots)$$

(iv) VCs from

$$\begin{aligned} & \{\mathcal{I}_1 \land \mathcal{I}_2 \land \mathsf{B} = w_2 \land 0 \leq \mathsf{I} \land \mathsf{I} \leq \mathsf{N-1} \} \\ & \mathsf{R} := (\mathsf{R}[\mathsf{O}] \bullet \mathsf{B} \uplus \mathsf{R}[\mathsf{2N-1} : \mathsf{N}]) \cap \mathsf{R}[\mathsf{N-1} : \mathsf{I}] \\ & \{ (\mathcal{I}_1 \land \mathcal{I}_2 \land \mathsf{B} = w_2) [\mathsf{I+1/I}] \} \end{aligned}$$

To show VC (i) assume

$$\begin{split} & {\sf R} = ({\sf W} \; {\sf N} \; 0) \frown w_1 \; \land \; {\sf B} = w_2 \; \land \; |w_1| \le {\sf N} \; \land \; |w_2| \le {\sf N} \; \land \; {\sf N} > 0 \\ & {\cal I}_1[0/{\sf I}] \; {\rm is:} \\ & w_1[{\sf N}-1:0] = (({\sf W} \; {\sf N} \; 0) \frown w_1[{\sf N}-1:0]) [{\sf N}-1:0] \\ & {\rm which \; follows \; from:} \\ & p < |w_2| \; \Rightarrow \; (w_1 \frown w_2) [p:q] \; = \; w_2[p:q] \\ & {\cal I}_2[0/{\sf I}] \; {\rm is:} \\ & {\sf V}((({\sf W} \; {\sf N} \; 0) \frown w_1[{\sf N}-1:0]) [2{\sf N}-1:{\sf N}]) = {\sf V}(w_1[0-1:0]) \times {\sf V}({\sf B}) \\ & {\rm which \; is \; equivalent \; to \; 0} = 0 \; {\rm because \; of \; the \; convention \; that \; {\sf V}({\sf A}[0-1:0]) \; {\rm is \; 0}, \; {\rm from \; which \; it \; follows \; that \; the \; {\sf RHS \; is \; 0}. \; {\sf The \; LHS \; can \; be \; simplified \; using:} \\ & q \ge |w_2| \; \Rightarrow \; (w_1 \frown w_2)[p:q] \; = \; w_1[p-|w_2|:q-|w_2|] \\ & w[|w|-1:0] \; = \; w \\ & {\sf V}({\sf W}\; n\; m) \; = \; m\; {\sf mod \; 2^n} \\ {\sf From \; this, \; it \; follows \; that:} \\ & {\sf V}((({\sf W}\; {\sf N}\; 0) \frown {\sf A}[{\sf N}-1:0])[2{\sf N}-1:{\sf N}]) \; = \; {\sf V}(({\sf W}\; {\sf N}\; 0)[{\sf N}-1:0]) \\ & = \; {\sf V}({\sf W}\; {\sf N}\; 0) \end{split}$$

= 0

(0)

To establish the second VC (ii) observe that  $\mathcal{I}_2[\mathbb{N}/\mathbb{I}]$  is

$V(\texttt{R[2N-1:N-N]}) = V(w_1[\texttt{N-1:0]}) \times V(\texttt{B})$

so if  $|w_1| \leq \mathbb{N}$  and  $B = w_2$  then clearly

$V(R[2N-1:0]) = V(w_1) \times V(w_2)$

The third VC (iii) is trivial (contradictory antecedent of an implication).

The final VC (iv) is the guts of the verification. The invariance of B is obvious. The remaining things to establish are:

$$\begin{aligned} \mathcal{I}_1 & \wedge & \mathcal{I}_2 & \wedge & \mathsf{B} = w_2 & \wedge & \mathsf{0} \leq \mathsf{I} & \wedge & \mathsf{I} \leq \mathsf{N} - \mathsf{1} \\ \Rightarrow \\ \mathsf{w}_1[\mathsf{N} - \mathsf{1} : \mathsf{I} + \mathsf{1}] &= \left( \left( \mathsf{R}[\mathsf{0}] \cdot \mathsf{B} \uplus \mathsf{R}[\mathsf{2}\mathsf{N} - \mathsf{1} : \mathsf{N}] \right) \cap \mathsf{R}[\mathsf{N} - \mathsf{1} : \mathsf{1}] \right) [\mathsf{N} - \mathsf{I} - \mathsf{2} : \mathsf{0}] \end{aligned}$$

VC4.2  $\mathcal{I}_1 \land \mathcal{I}_2 \land B = w_2 \land 0 \leq I \land I \leq N-1$

$V(((R[0] \bullet B \uplus R[2N-1:N]) \cap R[N-1:1])[2N-1:N-I-1]) = V(w_1[I:0]) \times V(B)$

VC4.1 follows from:

$$p < |w_2| \Rightarrow (w_1 \neg w_2)[p:q] = w_2[p:q]$$

$$(w[m:n])[p:q] = w[p+n:q+n]$$

Since:

$$(R[0] \bullet B \uplus R[2N-1:N]) \cap R[N-1:1])[N-I-2:0] = (R[N-1:1])[N-I-2:0]$$

= R[N-I-1:1]

= R[N-I-1:1]

= R[N-1-I:1]

and

$$\begin{aligned} \mathcal{I}_1 &\equiv w_1 [N-1:I] = R[N-1-I:0] \\ &\Rightarrow w_1 [N-1:I] [N-1-I:1] = R[N-1-I:0] [N-1-I:1] \\ &\Rightarrow w_1 [N-1:I+1] = R[N-1-I:1] \end{aligned}$$

To establish VC4.2 first observe that:

$$\begin{aligned} \mathcal{I}_1 &\equiv w_1 [\mathbb{N} - \mathbb{1} : \mathbb{I}] &= \mathbb{R} [\mathbb{N} - \mathbb{1} - \mathbb{I} : \mathbb{0}] \\ &\Rightarrow w_1 [\mathbb{N} - \mathbb{1} : \mathbb{I}] [\mathbb{0}] &= \mathbb{R} [\mathbb{N} - \mathbb{1} - \mathbb{I} : \mathbb{0}] [\mathbb{0}] \\ &\Rightarrow w_1 [\mathbb{I}] &= \mathbb{R} [\mathbb{0}] \end{aligned}$$

The cases I = 0 and I > 0 need to be considered separately. If I = 0 then:

$$\begin{aligned} \mathcal{I}_2 &\equiv \mathsf{V}(\mathsf{R}[\mathsf{2N}-\mathsf{1}:\mathsf{N}-\mathsf{I}]) = \mathsf{V}(w_1[\mathsf{I}-\mathsf{1}:\mathsf{0}]) \times \mathsf{V}(\mathsf{B}) \\ &\Rightarrow \mathsf{V}(\mathsf{R}[\mathsf{2N}-\mathsf{1}:\mathsf{N}]) = \mathsf{V}(w_1[\mathsf{0}-\mathsf{1}:\mathsf{0}]) \times \mathsf{V}(\mathsf{B}) \\ &\Rightarrow \mathsf{V}(\mathsf{R}[\mathsf{2N}-\mathsf{1}:\mathsf{N}]) = \mathsf{0} \times \mathsf{V}(\mathsf{B}) \\ &\Rightarrow \mathsf{V}(\mathsf{R}[\mathsf{2N}-\mathsf{1}:\mathsf{N}]) = \mathsf{0} \\ &\Rightarrow \mathsf{R}[\mathsf{2N}-\mathsf{1}:\mathsf{N}] = \mathsf{W} \ \mathsf{N} \ \mathsf{0} \end{aligned}$$

hence, assuming  $\mathcal{I}_1$ :

$$\begin{array}{l} \mathsf{V}((\mathsf{R}[\mathsf{O}] \cdot \mathsf{B} \uplus \mathsf{R}[2\mathsf{N}-1:\mathsf{N}]) \cap \mathsf{R}[\mathsf{N}-1:1]) [2\mathsf{N}-1:\mathsf{N}-\mathsf{I}-1]) = \mathsf{V}(w_1[\mathsf{I}:\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ \mathsf{V}((\mathsf{R}[\mathsf{O}] \cdot \mathsf{B} \uplus \mathsf{R}[2\mathsf{N}-1:\mathsf{N}]) \cap \mathsf{R}[\mathsf{N}-1:1]) [2\mathsf{N}-1:\mathsf{N}-1]) = \mathsf{V}(w_1[\mathsf{O}:\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ \mathsf{V}((w_1[\mathsf{O}] \cdot \mathsf{B} \uplus \mathsf{W} \ \mathsf{N} \ \mathsf{O})) \cap \mathsf{R}[\mathsf{N}-1:1]) [2\mathsf{N}-1:\mathsf{N}-1] = \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ \mathsf{V}(\mathsf{O} \cap (w_1[\mathsf{O}] \cdot \mathsf{B}) \cap \mathsf{R}[\mathsf{N}-1:1]) [2\mathsf{N}-1:\mathsf{N}-1]) = \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ (using: \ q \ge |w_2| \ \Rightarrow (w_1 \cap w_2) [p:q] = w_1[p-|w_2|:q-|w_2|]) \\ \mathsf{V}((\mathsf{O} \cap (w_1[\mathsf{O}] \cdot \mathsf{B})) [\mathsf{N}:\mathsf{O}]) = \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ \mathsf{V}((w_1[\mathsf{O}] \cdot \mathsf{B}) [\mathsf{N}-1:\mathsf{O}]) = \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ \mathsf{V}(u_1[\mathsf{O}] \cdot \mathsf{B}) [\mathsf{N}-1:\mathsf{O}]) = \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ \mathsf{Bv}(w_1[\mathsf{O}] \cdot \mathsf{N}) = \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \Leftrightarrow \\ \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) = \mathsf{Bv}(w_1[\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \\ \end{array}$$

If I>0 then as N>0 it follows that  $2N-1 \ge N-1$  and N-I-1 < N-1. Recall:

$$p \ge |w_2| \land q < |w_2| \Rightarrow (w_1 \neg w_2) [p:q] = w_1 [p-|w_2|:0] \neg w_2 [|w_2|-1:q]$$

hence, assuming  $\mathcal{I}_1$  and  $\mathcal{I}_2$ :

$$\begin{split} \mathsf{V}(((\mathsf{R}[\mathsf{O}] \bullet \mathsf{B} \uplus \mathsf{R}[2\mathsf{N}-1:\mathsf{N}]) \cap \mathsf{R}[\mathsf{N}-1:1])(2\mathsf{N}-1:\mathsf{N}-\mathsf{I}-1]) \\ &= \mathsf{V}((\mathsf{R}[\mathsf{O}] \bullet \mathsf{B} \uplus \mathsf{R}[2\mathsf{N}-1:\mathsf{N}])(\mathsf{N}:\mathsf{O}] \cap \mathsf{R}[\mathsf{N}-1:1](\mathsf{N}-2:\mathsf{N}-\mathsf{I}-1]) \\ &= \mathsf{V}((\mathsf{R}[\mathsf{O}] \bullet \mathsf{B} \uplus \mathsf{R}[2\mathsf{N}-1:\mathsf{N}])(\mathsf{N}:\mathsf{O}] \cap \mathsf{R}[\mathsf{N}-1:\mathsf{N}-\mathsf{I}]) \\ &= \mathsf{V}((\mathsf{R}[\mathsf{O}] \bullet \mathsf{B} \uplus \mathsf{R}[2\mathsf{N}-1:\mathsf{N}]) \cap \mathsf{R}[\mathsf{N}-1:\mathsf{N}-\mathsf{I}]) \\ &= 2^{\mathsf{I}} \times \mathsf{V}(\mathsf{R}[\mathsf{O}] \bullet \mathsf{B} \uplus \mathsf{R}[2\mathsf{N}-1:\mathsf{N}]) + \mathsf{V}(\mathsf{R}[\mathsf{N}-1:\mathsf{N}-\mathsf{I}]) \\ &= 2^{\mathsf{I}} \times \mathsf{V}(\mathsf{R}[\mathsf{O}] \bullet \mathsf{B}) + \mathsf{V}(\mathsf{R}[2\mathsf{N}-1:\mathsf{N}]) + \mathsf{V}(\mathsf{R}[\mathsf{N}-1:\mathsf{N}-\mathsf{I}]) \\ &= 2^{\mathsf{I}} \times \mathsf{V}(\mathsf{R}[\mathsf{O}] \bullet \mathsf{B}) + \mathsf{V}(\mathsf{R}[2\mathsf{N}-1:\mathsf{N}]) + \mathsf{V}(\mathsf{R}[\mathsf{N}-1:\mathsf{N}-\mathsf{I}]) \\ &= 2^{\mathsf{I}} \times \mathsf{V}(\mathsf{R}[\mathsf{O}] \bullet \mathsf{B}) + \mathsf{V}(\mathsf{R}[2\mathsf{N}-1:\mathsf{N}-\mathsf{I}]) \\ &= 2^{\mathsf{I}} \times \mathsf{V}(\mathsf{R}[\mathsf{O}] \bullet \mathsf{B}) + \mathsf{V}(\mathsf{R}[2\mathsf{N}-1:\mathsf{N}-\mathsf{I}]) \\ &= 2^{\mathsf{I}} \times \mathsf{V}(\mathsf{R}[\mathsf{O}] \bullet \mathsf{B}) + \mathsf{V}(\mathsf{M}_1[\mathsf{I}-1:\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \quad (\mathsf{by} \ \mathcal{I}_2) \\ &= 2^{\mathsf{I}} \times \mathsf{V}(\mathsf{R}[\mathsf{O}] \bullet \mathsf{B}) + \mathsf{V}(\mathsf{w}_1[\mathsf{I}-1:\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \quad (\mathsf{by} \ \mathcal{I}_1) \\ &= (2^{\mathsf{I}} \times \mathsf{Bv}(\mathsf{w}_1[\mathsf{I}]) + \mathsf{V}(\mathsf{w}_1[\mathsf{I}-1:\mathsf{O}])) \times \mathsf{V}(\mathsf{B}) \\ &= \mathsf{V}(\mathsf{w}_1[\mathsf{I}:\mathsf{O}]) \times \mathsf{V}(\mathsf{B}) \end{split}$$

This establishes VC4.2.

### 1.9 From programs to hardware

In the previous chapter a number of programs that did hardware-like things were verified. However, programs are not hardware. In this chapter we consider how programs can be interpreted as hardware. One possible interpretation is to 'unroll' a program into combinational logic. Consider the ripple-carry adder, for example.

```

FOR I := 0 UNTIL N-1 D0

BEGIN

SUM[I]:=A[I]⊕B[I]⊕CARRY;

CARRY:=(A[I]∧B[I])∨(CARRY∧(A[I]⊕B[I]));

END

```

If a particular value of N is fixed, then the program can be unrolled into the normal circuit for an adder. For example take N = 3 to get:

```

FOR I := 0 UNTIL 2 D0

BEGIN

SUM[I]:=A[I] ⊕B[I] ⊕CARRY;

CARRY:=(A[I] ∧B[I]) ∨ (CARRY∧(A[I] ⊕B[I]));

END

```

Assuming initially CARRY = F, the FOR-command unrolls to:

```

SUM[0] := A[0] \oplus B[0] \oplus F;

CARRY := (A[0] \land B[0]) \lor (F \land (A[0] \oplus B[0]));

SUM[1] := A[1] \oplus B[1] \oplus CARRY;

CARRY := (A[1] \land B[1]) \lor (CARRY \land (A[1] \oplus B[1]));

SUM[2] := A[2] \oplus B[2] \oplus CARRY;

CARRY := (A[2] \land B[2]) \lor (CARRY \land (A[2] \oplus B[2]));

```

Symbolically executing this (and doing some Boolean algebra simplification) yields:

These are now independent assignments that give explicit Boolean expressions for computing the values of SUM and CARRY directly in terms of the A[0], A[1], A[2], B[0], B[1] and B[2].

Clearly this process can be used to get the logic equations for adders of arbitrary bitwidths. The verification done earlier shows that any adder generated this way is correct.<sup>3</sup>

$<sup>^{3}</sup>$ This assumes that the original program is equivalent to the unrolled version. I hope this is intuitively clear. We will not attempt a more formal justification.

This interpretation of commands as hardware is sensible for the adder, but less so for the multipliers we considered. It is straightforward to unroll a multiplier into combinational logic, but the resulting Boolean expressions will be huge. Trying to evaluate them in one clock cycle is likely to make the cycle time too slow. The usual approach is to implement multipliers as sequential machines that compute the product over a number of cycles. For example, one might do the add and shift in a single cycle which would take N cycles. Alternatively, one might add and shift on separate cycles, taking 2N, presumably shorter, cycles. The decision of whether to implement a particular function as combinational or sequential logic, and if sequential, how much to do each cycle, is a decision which depends on engineering issues.

The view of a multiplier as computing a single state change from the initial values of the registers to the final values is quite abstract, but adequate for showing pure functional correctness (i.e. it does multiplication). Less abstract views are needed for timing analysis and other kinds of issues.

Modern HDLs like Verilog allow the designer to indicate how operations are scheduled into clock cycles. To illustrate this, we allow statements to be prefixed by  $\mathbf{Q}$ , which is called an *event control*. The multiplier that takes N cycles is:

FOR I := 0 UNTIL N-1 DO @R :=  $(R[0] \cdot B \uplus R[2N-1:N]) \cap R[N-1:1]$

and a multiplier that takes  $2\mathbb{N}$  cycles is:

```

FOR I := 0 UNTIL N-1 D0

BEGIN

@SUM := R[0]•B ⊎ R[2N-1:N];

@R := SUM∩R[N-1:1]

END

```

Note that SUM here needs to be 2N+1 bits wide.

In Verilog, for example, event controls can be more detailed, specifying that the subsequent commands are only triggered by particular kinds of events (e.g. rising edges or falling edges). However, at least for the time being, our toy HDL only has an abstract 'clock tick' events Q.

It is clear that programs with added event controls can still be reasoned about using Floyd Hoare logic, since the transformation from initial to final state is unchanged. The @'s merely serve to determine the intermediate states that occur at clock ticks. However, there are properties that one might want to hold but which cannot be expressed using Hoare-style correctness specifications, for example the fact that the variable B is not changed during the computation. Consider this silly program:

```

FOR I := 0 UNTIL N-1 D0

BEGIN

@SUM := R[0].B \U2204 R[2N-1:N];

B := ¬B;

@R := SUM∩R[N-1:1];

B := ¬B;

END

```

Here  $\neg B$  denotes the negation of every bit of B. This program takes 2N cycles and (as  $\neg \neg B = B$ ) it has the same overall effect. However, B keeps changing throughout the computation and this cannot be expressed using Hoare triples  $\{P\}C\{Q\}$ . Often, e.g. in connection with handshake protocols, one wants to ensure variables stay constant throughout parts of the computation, and this cannot ve verified using Floyd-Hoare logic. Later in this course we will meet *temporal logic* which enables properties of intermediate states to be specified.

HDL synthesis tools can compile imperative programs to state machines that can be directly implemented in hardware. One can thus verify hardware by verifying HDL code segments using Floyd-Hoare logic prior to synthesis. Of course, this assumes hardware synthesis is correct!

In the next chapter we look at describing hardware structure and behaviour in directly higher order logic. We will look at the ripple-carry adder and add-shift multiplier again and compare their verification as source HDL with their verification as directly modelled hardware.

# Describing Hardware Directly in Higher Order Logic

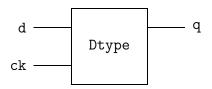

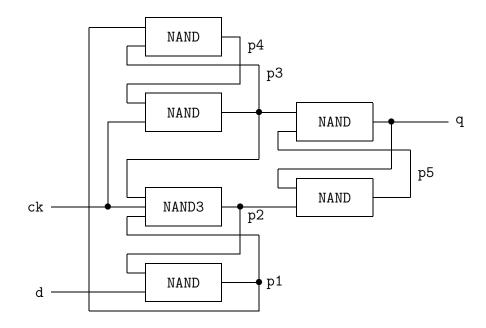

It is shown how higher order logic can be used both as a hardware description language and as a formalism for proving that designs meet their specifications. Examples are given which illustrate various specification and verification techniques. These include a CMOS inverter, a CMOS full adder, an n-bit ripplecarry adder, a sequential multiplier and an edge-triggered Dtype register.

### 2.1 Representing behaviour with predicates

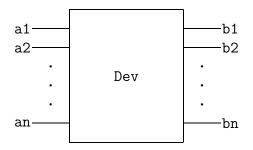

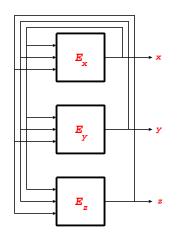

A device is a 'black box' with a specified behaviour; for example:

This device is called **Dev** and has external lines a1, a2, ..., am, b1, b2, ..., bn. These lines correspond to the 'pins' of an integrated circuit. When the device is in operation each line has a value drawn from some set of possible values. Different kinds of device are modelled with different sets of values. The behaviour of device **Dev** is specified by defining a predicate **Dev** (with m+n arguments) such that  $Dev(a_1, a_2, \ldots, a_m, b_1, b_2, \ldots, b_n)$  holds if and only if  $a_1, a_2, \ldots, a_m, b_1, b_2, \ldots, b_n$  are allowable values on the corresponding lines of **Dev**.

The following font conventions will be used:

• Physical objects like devices and lines will be written in typewriter font.

- Mathematical variables will be written in *italic* font.

- Mathematical constants, (e.g. predicate and function constants) will be written in sans serif font.

The same letter will be used for a physical object and its mathematical representation. Thus, for example, l will range over the values allowed at line 1, and **Dev** denotes the predicate describing the behaviour of device **Dev**.

We now describe two examples that illustrate the use of predicates to specify behaviour. In the first of these examples the values on lines are modelled with truth-values. In the second example the values on lines are modelled with functions, and consequently the predicate used to specify the behaviour of the device is higher-order.

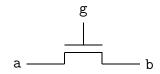

#### 2.1.1 A delayless switch

Zero-delay combinational devices can be modelled by taking the boolean values T and F as the allowed values on their lines. An example is a switch:

The intended behaviour of this is that a is connected to b if g has the value T and a and b are not connected if g has the value F. This behaviour can be represented by the predicate Switch defined by:

$$\mathsf{Switch}(g, a, b) \equiv (g \Rightarrow (a = b))$$

The condition Switch(g, a, b) holds if and only if whenever g is true then a and b are equal. For example, Switch(T, F, F) holds because  $T \Rightarrow (F=F)$  is true, and Switch(F, T, F) holds because  $F \Rightarrow (T=F)$  is true, but Switch(T, T, F) does not hold because  $T \Rightarrow (T=F)$  is false.

#### 2.1.2 An inverter with delay

The values occurring on the lines of devices may vary over time. When this happens, their behaviour must be represented by predicates whose arguments are 'time varying values'. Such values correspond to 'waveforms' and can be modelled by functions of time. For example, the behaviour of an inverter with a delay of  $\delta$  units of time can be specified with a predicate **Invert** defined by:

$$\mathsf{Invert}(i, o) \equiv \forall t. \ o(t + \delta) = \neg i(t)$$

Here the values on lines i and o are functions i and o which map times (represented by numbers) to values (represented by booleans). These functions are in the **Invert** relation if and only if for all times t, the value of o at time  $t+\delta$  equals the value of i at time t.

### 2.2 Representing circuit structure with predicates

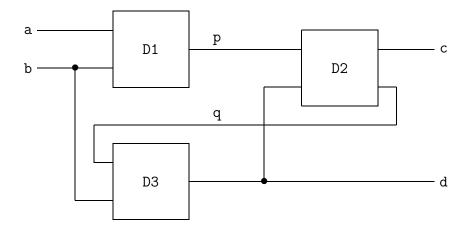

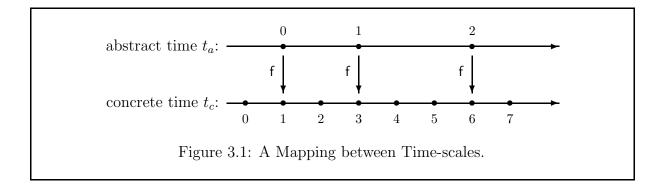

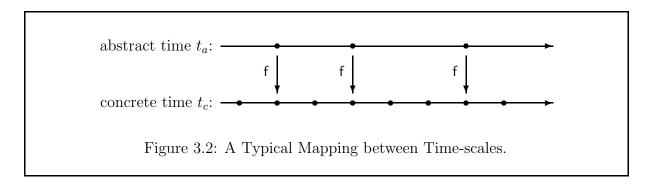

Consider the following structure (called D):

This device is built by connecting together three component devices D1, D2 and D3. The external lines of D are a, b, c and d. The lines p and q are internal and are not connected to the 'outside world'. (External lines might correspond to the pins of an integrated circuit, and internal lines to tracks.)

Suppose the behaviours of D1, D2 and D3 are specified by predicates  $D_1$ ,  $D_2$  and  $D_3$  respectively. How can we derive the behaviour of the system D shown above? Each device constrains the values on its lines. If a, b and p denote the values on the lines a, b and p, then D1 constrains these values so that  $D_1(a, b, p)$  holds. To get the constraint imposed by the whole device D we just conjoin (i.e.  $\wedge$ -together) the constraints imposed by D1, D2 and D3; the combined constraint is thus:

$$\mathsf{D}_1(a,b,p) \land \mathsf{D}_2(p,d,c,q) \land \mathsf{D}_3(q,b,d)$$

This expression constrains the values on both the external lines a, b, c and d and the internal lines p and q. If we regard D as a 'black box' with the internal lines invisible, then we are really only interested in what constraints are imposed on its external lines. The variables a, b, c and d will denote possible values at the external lines a, b, c and d if and only if the conjunction above holds for some values p and q. We can therefore define a predicate D representing the behaviour of D by:

$$\mathsf{D}(a, b, c, d) \equiv \exists p \ q. \ \mathsf{D}_1(a, b, p) \land \mathsf{D}_2(p, d, c, q) \land \mathsf{D}_3(q, b, d)$$

Thus we see that the behaviour corresponding to a circuit is got by conjoining the constraints corresponding to the components, and then existentially quantifying the variables corresponding to the internal lines. This technique of representing circuit diagrams in logic is fairly well known. Other ways of representing structure in logic are also possible. There is a nice paper on this by William Clocksin entitled *Logic Programming and the Specification of Circuits* (Computer Laboratory Technical Report No. 72, 1985).

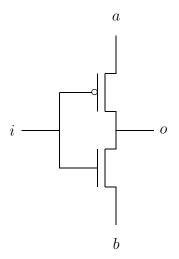

### 2.3 A CMOS inverter

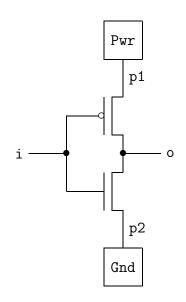

The standard CMOS implementation of an inverter is:

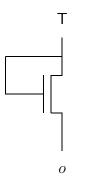

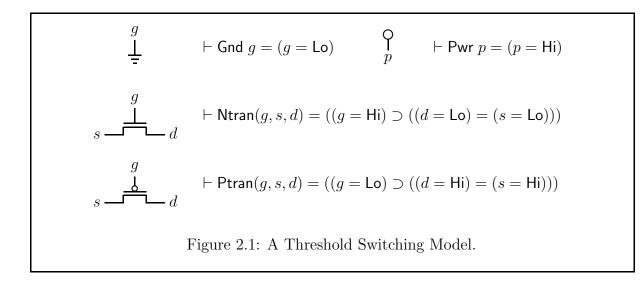

### 2.3.1 Specification of the components

The inverter shown above can be viewed as a structure built out of four components: a power source, a ground, an n-transistor and a p-transistor.

#### 2.3.1.1 Power