Datorsystemet

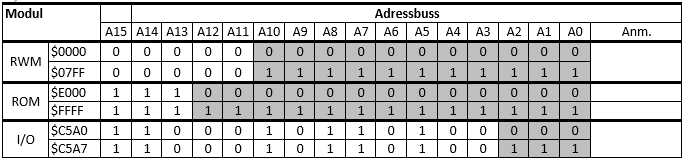

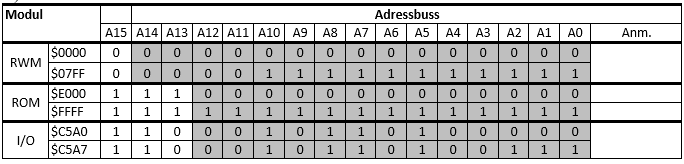

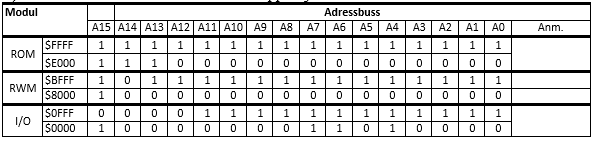

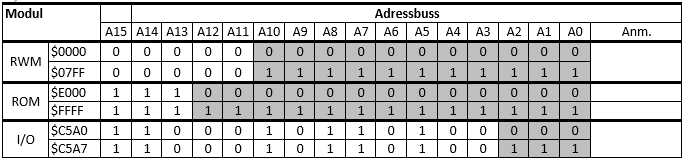

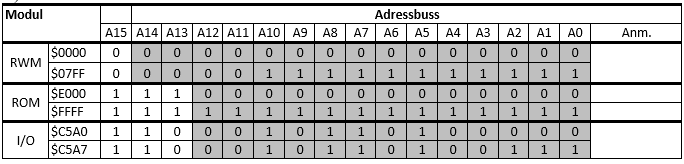

10.1 Ett datorsystem med 64 kbyte adressrymd ska konstrueras. Konstruera adressavkodningen för följande:

2 kbyte RWM från adress 0

8 kbyte ROM på de högsta adresserna

En I/O-area på 8 byte med start på adress $C5A0

Du har tillgång till

8 kbyte ROM-modul

2 kbyte RWM-modul

a) Använd fullständig adressavkodning

b) Använd ofullständig adressavkodning

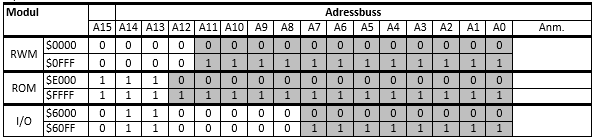

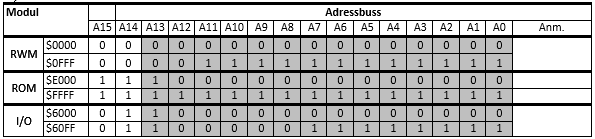

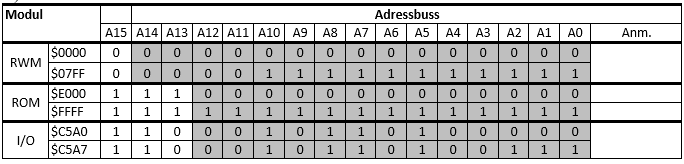

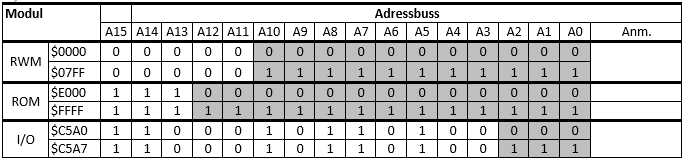

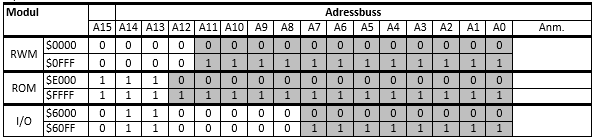

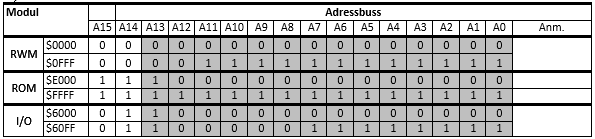

10.2 Ett datorsystem med 64 kbyte adressrymd ska konstrueras. Konstruera adressavkodningen för följande:

4 kbyte RWM från adress 0

8 kbyte ROM på de högsta adresserna

En I/O-area på 256 byte med start på adress $6000

Du har tillgång till

8 kbyte ROM-modul

4 kbyte RWM-modul

a) Använd fullständig adressavkodning

b) Använd ofullständig adressavkodning

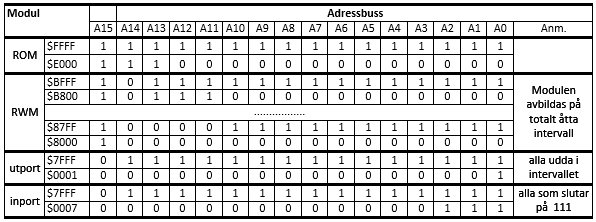

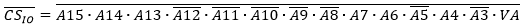

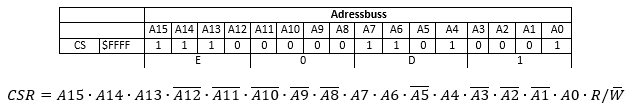

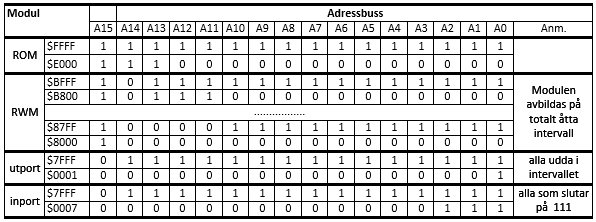

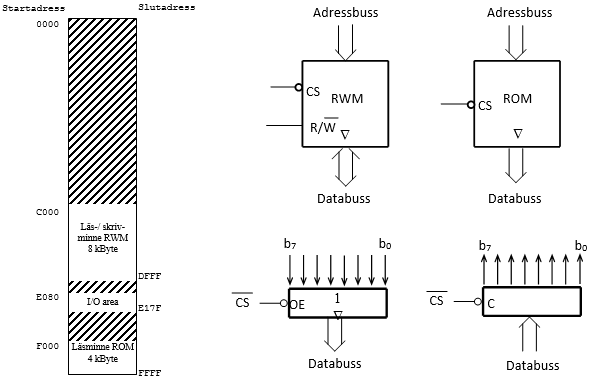

10.3 I ett datorsystem, med synkron buss, 64 kbyte adressrymd och med 8 bitars databuss används en 16 kbyte ROM-kapsel för att lagra program och en 2 kbyte RWM-kapsel för att lagra variabler. Dessutom används en 8-bitars "three-state"-buffert som inport och ett 8-bitars register som utport. I nedanstående figur visas hur "chip-select"-avkodningen för dessa är utförd.

a) Redogör för var i adressrummet processorn kan läsa eller skriva i

de olika enheterna. Alla adresser där en enhet kan nås skall redovisas.

b) Konstruktören upptäcker vid provning av systemet att märkliga saker ibland händer vid läsning av indata från inporten. Hjälp konstruktören reda ut vad som händer.

Vid läsning av inporten på adresserna 0xxx xxxx xxxx x111 så adresseras också utporten

eftersom inte R/W-signalen används i dess avkodning.

Data som läses från inporten skrivs då också i utporten.

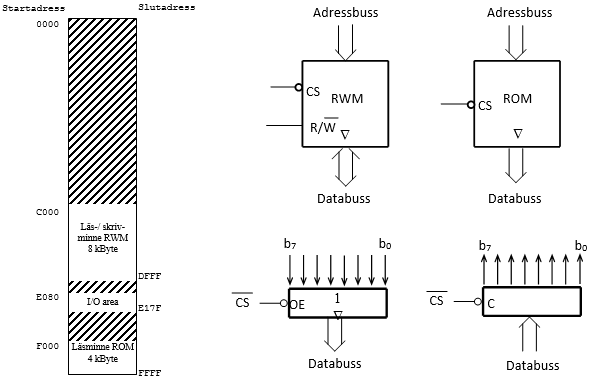

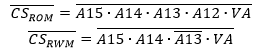

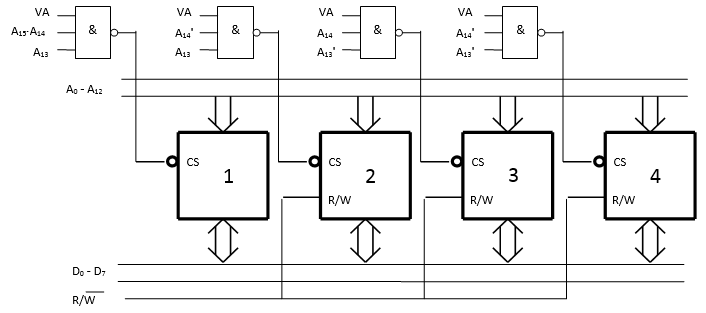

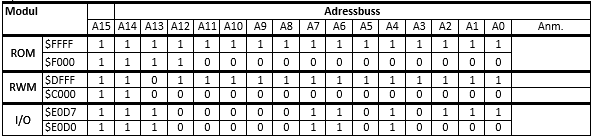

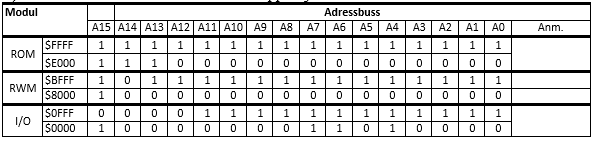

10.4 Ett datorsystem, med synkron buss, 64 kbyte adressrymd och med 8 bitars databuss ska konstrueras. Centralenheten genererar en VA signal för att indikera att innehållet på adressbussen är giltigt och en R/W-signal för att indikera läsning respektive skrivning. Figuren nedan visar hur adressrummet ska användas (alla adresser anges på hexadecimal form). Systemet skall bestyckas med 1 st. 8 kbyte RWM-kapsel, 1 st. 4 kbyte ROM-kapsel, 4 st. inportar och 4 st. utportar. Modulernas modeller ges också i figuren. Med tanke på framtida utbyggnad skall alla moduler, som ansluts till adressbussen, vara fullständigt avkodade.

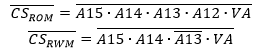

a) Konstruera “chip select”-logiken för de två minneskapslarna.

b) Konstruera “chip select”-logiken för in- och utportarna så att de ligger på adresserna $E0D0 - $E0D7, med inportar på udda adresser och utportar på jämna. Konstruktionen skall ha en gemensam del som skapar “chip select” för hela I/O arean.

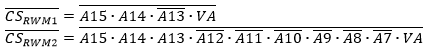

CS-signalerna bildas ur de för respektive modul konstanta adressdelarna, som grindas med VA-signalen.

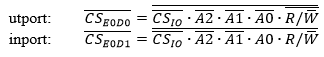

För in- och utportarna skapas den gemensamma CS-signalen:

CS-signalerna för respektive port blir nu:

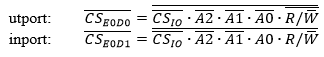

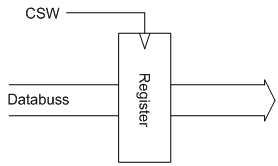

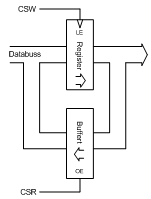

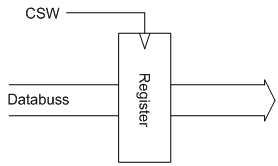

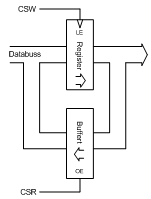

10.5 En utport där gränssnittet utgörs av endast ett register är normalt inte läsbar. Föreslå hur en icke-läsbar utport på adress $E0D1 skall "byggas om" så att den också blir läsbar.

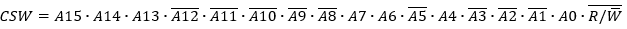

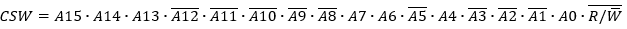

I figuren förutsätts CSW vara en korrekt bildad CS-signal för porten, visa hur CSW bildas. Visa även den kompletta adressavkodningslogiken.

Placera en ”inport” i form av en buffert, på samma adress, men med en CSR (ChipSelectRead)

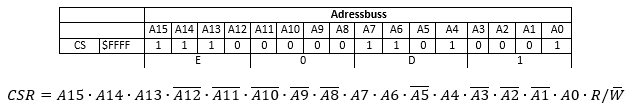

CSR och CSW är aktivt höga:

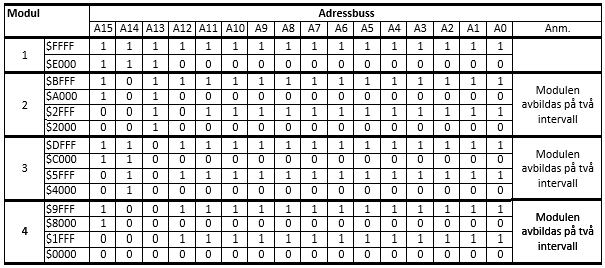

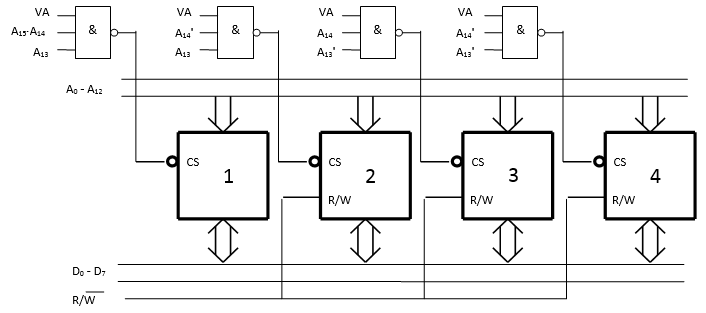

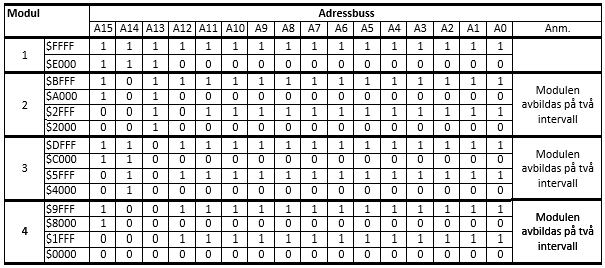

10.6 I ett datorsystem, med synkron buss, 64 kbyte adressrymd och med 8 bitars databuss har minneskretsar kopplats enligt följande figur. Primärminnet utgörs av ROM och RWM uppdelat på fyra minneskapslar.

a) Vad betyder förkortningarna ROM och RWM?

ROM ( Read Only Memory ) minne som enbart är läsbart. RWM ( Read Write Memory ) minne som är både läsbart och skrivbart.

b) Hur stort är systemets ROM respektive RWM?

Man ser att varje minneskapsel har 13 adressledningar, A0 - A12, som insignaler. Det innebär att varje kapsel innehåller 213 ord = 8 kbyte. Man ser också att en av kapslarna, nr 1) är av ROM-typ, ty den använder ej R/W-signalen. Datorn har således 8 kbyte ROM och 24 kbyte RWM.

c) Vilka adressområden (hexadecimalt) upptar respektive minneskapsel (1 t o m 4)?

Minneskapslarna upptar följande adressområden:

d) Vilken roll har användningen av signalen ”VA” vid adresseringen av en minneskapsel?

VA = 1 (Valid Memory Address) anger att adressbussens värde är stabilt och därför används denna signal för att grinda adresserna till minnet. Då kommer de adresser som finns ut på bussen under tiden som adressledningar håller på att ändras aldrig att nå primärminnet.

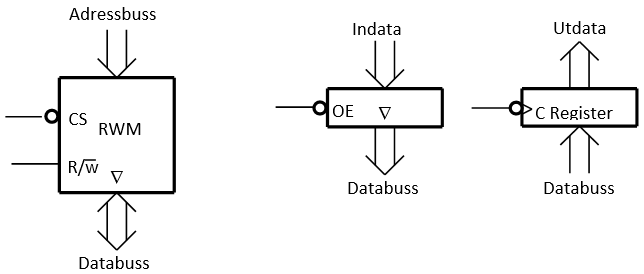

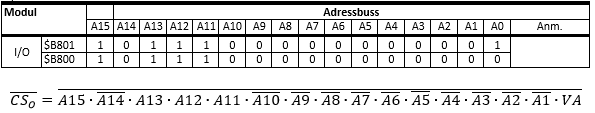

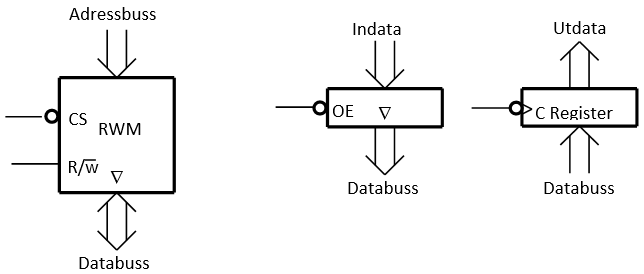

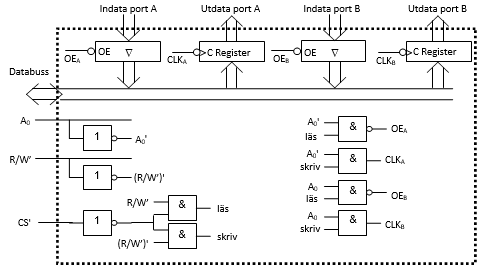

10.7 Föreställ dig en I/O-modul för vilken RWM-modulen till vänster i figuren har stått modell.

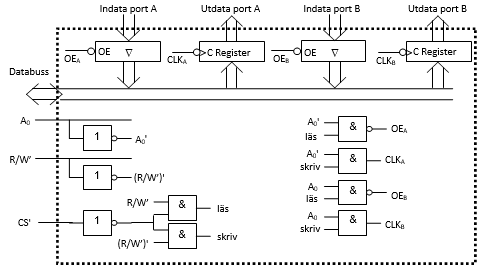

Dvs. de har samma insignal- och utsignalstruktur mot en processorbuss. I I/O-modulen finns två inportar (ingångs-buffertar) och två utportar (utgångsregister) av den typ som visas till höger i figuren. Den tar upp två adresser, vilket innebär att på varje adress finns en inport och en utport.

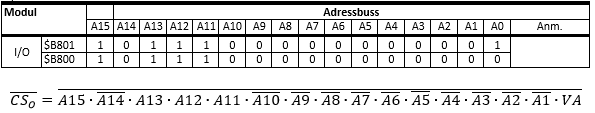

a) I ett mikrodatorsystem, med synkron buss, 64 kbyte adressrymd och med 8 bitars databuss har I/O-modulen adresserna $B800 och $B801. Visa hur modulen är ansluten till centralenheten. Adressavkodningen är fullständig. Signalerna VA respektive R/W används för att indikera giltig adress respektive läs- eller skriv- /operation.

b) Visa hur I/O-modulen principiellt är kopplad internt, dvs. hur de två inportarna och de två utportarna tillsammans med annan logik är ihopkopplade så att modulen kan representeras med en RWM-liknande modul.

I/O-modulens interna struktur bör utformas på följande sätt:

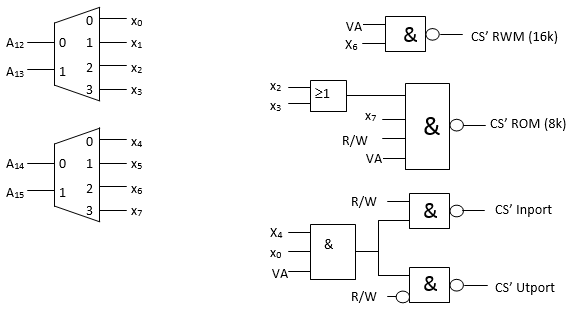

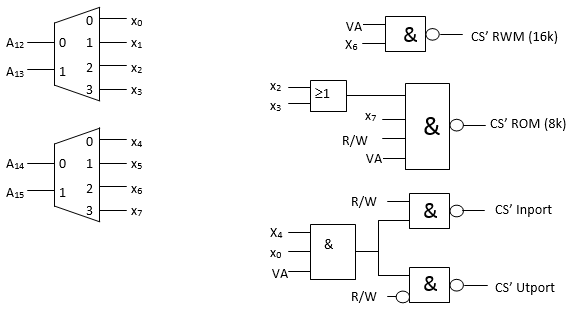

10.8 I CS-avkodningen för ett datorsystem med 16 bitars adressbuss används två st. ”2 till 4”- avkodare enligt följande figur.

Insignalerna till avkodarna är adressbitar från adressbussen. Utsignalerna (x0 – x7) från avkodarna används för att bilda CS-signalerna.

a) Analysera kopplingen och bestäm på vilka adresser minnesmodulerna och portarna är placerade.

Minnesmodulerna i adressrum M tar upp följande adressområden:

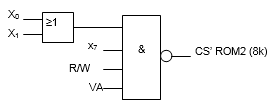

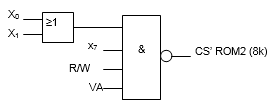

b) Man vill placera en andra ROM-modul i direkt anslutning till den som redan finns. Visa CS-logiken och adressintervallet för denna modul.

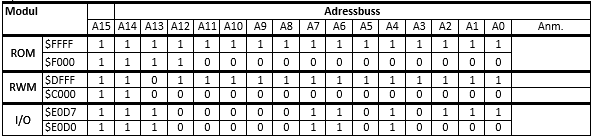

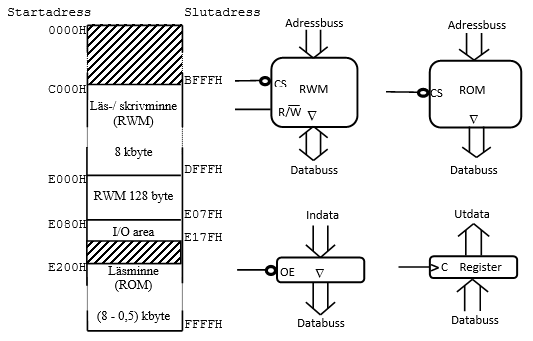

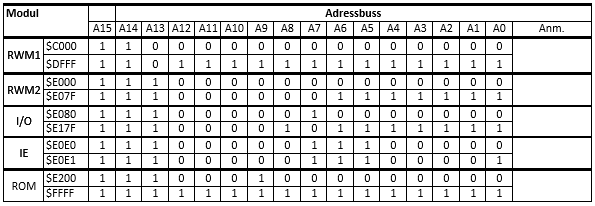

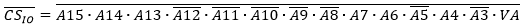

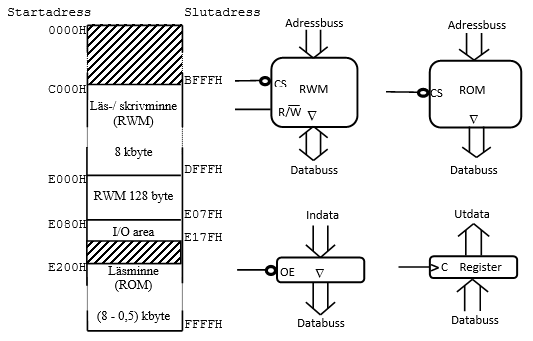

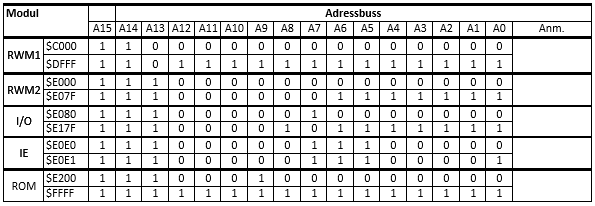

10.9 Adressrummet för ett givet datorsystem, med synkron buss, 64 kbyte adressrymd och med 8 bitars databuss visas i bilden till vänster i figuren. Centralenheten genererar en VA signal för att indikera att innehållet på adressbussen är giltigt och en R/W-signal för att indikera läsning respektive skrivning.

Som läs-/skrivminne används 2 st. RWM-moduler om vardera 8 kbyte och 128 byte. Som läsminne används 1 st. ROM-modul om 8 kbyte. In- och utportar är och kan (vid utökning) placeras i den givna I/O-arean. Modeller av dessa moduler och portar ges också till höger i figuren. Användningen av I/O-arean kan variera från en tillämpning till en annan. Man skall med lätthet kunna byta ut och lägga till portar.

Adressavkodningen för enheter i denna area bör därför vara indelad i två steg där det första steget avkodar adresser inom själva I/O-arean och det andra steget dessutom väljer ett specifikt gränssnitt. All avkodning nedan skall vara fullständig och får göras med standardgrindar (INVERTERARE, OCH, ELLER, NAND, NOR, XOR).

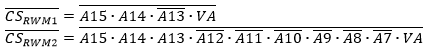

a) Konstruera adressavkodningslogiken för RWM-modulerna.

Minnesmodulerna och I/O-arean i adressrummet tar upp följande adressområden:

CS-signalerna bildas enligt:

b) Konstruera en tvåstegs adressavkodare för inplaceringen av ett gränssnitt ”IE” som upptar adresserna $E0E0 och $E0E1.

Vid läsning av inporten på adresserna 0xxx xxxx xxxx x111 så adresseras också utporten

eftersom inte R/W-signalen används i dess avkodning.

Data som läses från inporten skrivs då också i utporten.

Vid läsning av inporten på adresserna 0xxx xxxx xxxx x111 så adresseras också utporten

eftersom inte R/W-signalen används i dess avkodning.

Data som läses från inporten skrivs då också i utporten.

a) Konstruera “chip select”-logiken för de två minneskapslarna.

b) Konstruera “chip select”-logiken för in- och utportarna så att de ligger på adresserna $E0D0 - $E0D7, med inportar på udda adresser och utportar på jämna. Konstruktionen skall ha en gemensam del som skapar “chip select” för hela I/O arean.

a) Konstruera “chip select”-logiken för de två minneskapslarna.

b) Konstruera “chip select”-logiken för in- och utportarna så att de ligger på adresserna $E0D0 - $E0D7, med inportar på udda adresser och utportar på jämna. Konstruktionen skall ha en gemensam del som skapar “chip select” för hela I/O arean.

CS-signalerna bildas ur de för respektive modul konstanta adressdelarna, som grindas med VA-signalen.

CS-signalerna bildas ur de för respektive modul konstanta adressdelarna, som grindas med VA-signalen.

För in- och utportarna skapas den gemensamma CS-signalen:

För in- och utportarna skapas den gemensamma CS-signalen:

CS-signalerna för respektive port blir nu:

CS-signalerna för respektive port blir nu:

Placera en ”inport” i form av en buffert, på samma adress, men med en CSR (ChipSelectRead)

Placera en ”inport” i form av en buffert, på samma adress, men med en CSR (ChipSelectRead)

CSR och CSW är aktivt höga:

CSR och CSW är aktivt höga:

a) Vad betyder förkortningarna ROM och RWM?

ROM ( Read Only Memory ) minne som enbart är läsbart. RWM ( Read Write Memory ) minne som är både läsbart och skrivbart.

b) Hur stort är systemets ROM respektive RWM?

Man ser att varje minneskapsel har 13 adressledningar, A0 - A12, som insignaler. Det innebär att varje kapsel innehåller 213 ord = 8 kbyte. Man ser också att en av kapslarna, nr 1) är av ROM-typ, ty den använder ej R/W-signalen. Datorn har således 8 kbyte ROM och 24 kbyte RWM.

c) Vilka adressområden (hexadecimalt) upptar respektive minneskapsel (1 t o m 4)?

Minneskapslarna upptar följande adressområden:

a) Vad betyder förkortningarna ROM och RWM?

ROM ( Read Only Memory ) minne som enbart är läsbart. RWM ( Read Write Memory ) minne som är både läsbart och skrivbart.

b) Hur stort är systemets ROM respektive RWM?

Man ser att varje minneskapsel har 13 adressledningar, A0 - A12, som insignaler. Det innebär att varje kapsel innehåller 213 ord = 8 kbyte. Man ser också att en av kapslarna, nr 1) är av ROM-typ, ty den använder ej R/W-signalen. Datorn har således 8 kbyte ROM och 24 kbyte RWM.

c) Vilka adressområden (hexadecimalt) upptar respektive minneskapsel (1 t o m 4)?

Minneskapslarna upptar följande adressområden:

d) Vilken roll har användningen av signalen ”VA” vid adresseringen av en minneskapsel?

VA = 1 (Valid Memory Address) anger att adressbussens värde är stabilt och därför används denna signal för att grinda adresserna till minnet. Då kommer de adresser som finns ut på bussen under tiden som adressledningar håller på att ändras aldrig att nå primärminnet.

d) Vilken roll har användningen av signalen ”VA” vid adresseringen av en minneskapsel?

VA = 1 (Valid Memory Address) anger att adressbussens värde är stabilt och därför används denna signal för att grinda adresserna till minnet. Då kommer de adresser som finns ut på bussen under tiden som adressledningar håller på att ändras aldrig att nå primärminnet.

Dvs. de har samma insignal- och utsignalstruktur mot en processorbuss. I I/O-modulen finns två inportar (ingångs-buffertar) och två utportar (utgångsregister) av den typ som visas till höger i figuren. Den tar upp två adresser, vilket innebär att på varje adress finns en inport och en utport.

a) I ett mikrodatorsystem, med synkron buss, 64 kbyte adressrymd och med 8 bitars databuss har I/O-modulen adresserna $B800 och $B801. Visa hur modulen är ansluten till centralenheten. Adressavkodningen är fullständig. Signalerna VA respektive R/W används för att indikera giltig adress respektive läs- eller skriv- /operation.

Dvs. de har samma insignal- och utsignalstruktur mot en processorbuss. I I/O-modulen finns två inportar (ingångs-buffertar) och två utportar (utgångsregister) av den typ som visas till höger i figuren. Den tar upp två adresser, vilket innebär att på varje adress finns en inport och en utport.

a) I ett mikrodatorsystem, med synkron buss, 64 kbyte adressrymd och med 8 bitars databuss har I/O-modulen adresserna $B800 och $B801. Visa hur modulen är ansluten till centralenheten. Adressavkodningen är fullständig. Signalerna VA respektive R/W används för att indikera giltig adress respektive läs- eller skriv- /operation.

b) Visa hur I/O-modulen principiellt är kopplad internt, dvs. hur de två inportarna och de två utportarna tillsammans med annan logik är ihopkopplade så att modulen kan representeras med en RWM-liknande modul.

I/O-modulens interna struktur bör utformas på följande sätt:

b) Visa hur I/O-modulen principiellt är kopplad internt, dvs. hur de två inportarna och de två utportarna tillsammans med annan logik är ihopkopplade så att modulen kan representeras med en RWM-liknande modul.

I/O-modulens interna struktur bör utformas på följande sätt:

Insignalerna till avkodarna är adressbitar från adressbussen. Utsignalerna (x0 – x7) från avkodarna används för att bilda CS-signalerna.

a) Analysera kopplingen och bestäm på vilka adresser minnesmodulerna och portarna är placerade.

Minnesmodulerna i adressrum M tar upp följande adressområden:

Insignalerna till avkodarna är adressbitar från adressbussen. Utsignalerna (x0 – x7) från avkodarna används för att bilda CS-signalerna.

a) Analysera kopplingen och bestäm på vilka adresser minnesmodulerna och portarna är placerade.

Minnesmodulerna i adressrum M tar upp följande adressområden:

b) Man vill placera en andra ROM-modul i direkt anslutning till den som redan finns. Visa CS-logiken och adressintervallet för denna modul.

b) Man vill placera en andra ROM-modul i direkt anslutning till den som redan finns. Visa CS-logiken och adressintervallet för denna modul.

a) Konstruera adressavkodningslogiken för RWM-modulerna.

Minnesmodulerna och I/O-arean i adressrummet tar upp följande adressområden:

a) Konstruera adressavkodningslogiken för RWM-modulerna.

Minnesmodulerna och I/O-arean i adressrummet tar upp följande adressområden:

CS-signalerna bildas enligt:

CS-signalerna bildas enligt:

b) Konstruera en tvåstegs adressavkodare för inplaceringen av ett gränssnitt ”IE” som upptar adresserna $E0E0 och $E0E1.

b) Konstruera en tvåstegs adressavkodare för inplaceringen av ett gränssnitt ”IE” som upptar adresserna $E0E0 och $E0E1.